# KONZEPTIONIERUNG, PORTIERUNG UND EVALUIERUNG EINES ECHTZEIT-ETHERCAT- FELDBUS-MAINDEVICES

---

auf einem Mikrocontroller ohne Betriebssystem

# Masterarbeit

zur Erlangung des akademischen Grades

Master of Engineering

im Studiengang

Informations- und Kommunikationstechnik

am

Fachbereich 1: Energie und Information

an der

Hochschule für Technik und Wirtschaft Berlin (HTW Berlin)

erstellt von

Marcel Beausencourt

erstellt am

Deutschen Zentrum für Luft- und Raumfahrt e.V. (DLR)

Institut

Robotik und Mechatronik Zentrum (RMC)

Abteilung

Autonomie und Fernprogrammierung (AUF)

Erstgutachter

Prof. Dr. Thomas Scheffler (HTW Berlin)

Zweitgutachter

Robert Burger (DLR)

Oberpfaffenhofen, den 12. April 2025

Deutsches Zentrum für Luft- und Raumfahrt e.V.

Robotik und Mechatronik Zentrum

Prof. Dr. Alin Albu-Schäffer, Dr.-Ing. Johann Bals, Prof. Dr. rer. nat. Heinz-Wilhelm Hübers

Münchener Straße 20

82234 Weßling

Tel: +49 8153 28-3689

Fax: +49 8153 28-1134

Web: <https://www.dlr.de/rm>

Marcel Beausencourt

Tel: +49 8153 28-3305

Mail: marcel.beausencourt@dlr.de

## Dokument-Identifikation:

## Abstract

Diese Masterarbeit erläutert alle Schritte, die nötig sind, um die beiden Bibliotheken `libethercat` und `libosal` vom Betrieb in einem Betriebssystem auf einen STM32-Mikrocontroller ohne Betriebssystem zu portieren. Diese Arbeit ist als Machbarkeitsstudie zur Portierung zu verstehen.

EtherCAT wird als Kommunikationsstandard am Deutschen Zentrum für Luft- und Raumfahrt in vielen Robotersystemen eingesetzt, um Daten über deren Peripherie (v.a. Sensoren und Aktoren) zu sammeln, diese zu konfigurieren und zu steuern. Die Bibliothek `libethercat` stellt Funktionen bereit, um das EtherCAT MainDevice auf der gegebenen Hardware zu implementieren. Die Bibliothek `libosal` stellt Funktionen bereit, welche den Betrieb von der Hardware und den Zugriff auf Betriebssystemressourcen abstrahieren.

Es wird eine Einführung in bestimmte Aspekte von Echtzeit, Feldbussen und des EtherCAT Standards gegeben, welche wichtig für die Realisierung des MainDevices sind. Daraufhin werden sowohl Hardware als auch Software analysiert und die wichtigsten Punkte hinsichtlich einer Konzeptionierung herausgearbeitet.

Nötige Anpassungen und Vorarbeiten wie bspw. das Umlöten der Hardware und Konfiguration der Hardware-Module des STM32 werden fokussiert dargestellt, da diese unerlässlich für die Portierung waren. Änderungen an den beiden Bibliotheken werden dargestellt, um ersichtlich zu machen, welche Anpassungen nötig waren, um den Betrieb auf einem STM32 zu gewährleisten. Dazu zählen auch Änderungen in hardware-spezifischen Files, die teilweise erst bei Inbetriebnahme des EtherCAT MainDevices und den angeschlossenen SubDevices auffielen.

Es wurden zeitliche Messungen und Plots zu je zwei verschiedenen Netzwerktopologien auf dem STM32 angefertigt, bevor diese mit Messungen von einem Linux-PC als MainDevice verglichen wurden. Die Netzwerktopologien unterscheiden sich in Art und Anzahl der SubDevices. Anschließend wird eine Bewertung der Implementierung hinsichtlich der Vergleichsmessungen gegeben.

Abschließend wird diese Arbeit zusammengefasst und ein Ausblick auf zukünftige Arbeiten gegeben, die auf diese Arbeit folgen können, bevor Schlussfolgerungen zur gesamten Arbeit gemacht werden.

# Inhaltsverzeichnis

|                                                                         |             |

|-------------------------------------------------------------------------|-------------|

| <b>Abstract</b>                                                         | <b>I</b>    |

| <b>Inhaltsverzeichnis</b>                                               | <b>V</b>    |

| <b>Abbildungsverzeichnis</b>                                            | <b>VIII</b> |

| <b>Tabellenverzeichnis</b>                                              | <b>IX</b>   |

| <b>Codeverzeichnis</b>                                                  | <b>XII</b>  |

| <b>1. Einleitung</b>                                                    | <b>1</b>    |

| 1.1. Motivation . . . . .                                               | 1           |

| 1.2. Zielsetzung und Aufgabenstellung . . . . .                         | 2           |

| 1.3. Aufbau der Arbeit . . . . .                                        | 3           |

| <b>2. Grundlagen</b>                                                    | <b>5</b>    |

| 2.1. Echtzeitsysteme . . . . .                                          | 5           |

| 2.1.1. Scheduling in Echtzeitsystemen . . . . .                         | 5           |

| 2.1.2. Rechtzeitigkeit . . . . .                                        | 6           |

| 2.1.3. Deadlines . . . . .                                              | 7           |

| 2.1.4. Tasks . . . . .                                                  | 8           |

| 2.1.5. Gleichzeitigkeit und Auslastung . . . . .                        | 9           |

| 2.1.6. Determinismus . . . . .                                          | 9           |

| 2.1.7. Zuverlässigkeit-/Performancebedingungen . . . . .                | 10          |

| 2.1.8. Umgebung . . . . .                                               | 10          |

| 2.2. Feldbusse . . . . .                                                | 10          |

| 2.3. EtherCAT . . . . .                                                 | 12          |

| 2.3.1. Funktionsprinzip . . . . .                                       | 12          |

| 2.3.2. EtherCAT Packet Flow . . . . .                                   | 13          |

| 2.3.3. Das EtherCAT Protokoll . . . . .                                 | 14          |

| 2.3.4. Flexible Topologie . . . . .                                     | 18          |

| 2.3.5. Distributed Clocks für High-Precision Synchronisierung . . . . . | 19          |

| 2.3.6. Diagnose und Fehlerlokalisierung . . . . .                       | 21          |

---

|                                                                   |           |

|-------------------------------------------------------------------|-----------|

| 2.3.7. Anforderung an hohe Verfügbarkeit . . . . .                | 22        |

| 2.3.8. Mailbox und Kommunikationsprofile . . . . .                | 23        |

| 2.3.9. Fieldbus Memory Management Unit . . . . .                  | 24        |

| 2.3.10. SyncManager . . . . .                                     | 25        |

| 2.3.11. Implementierung von EtherCAT Interfaces . . . . .         | 26        |

| 2.3.12. EtherCAT State Machine . . . . .                          | 29        |

| 2.3.13. Working Counter . . . . .                                 | 32        |

| 2.3.14. Wichtige Kommandos . . . . .                              | 32        |

| 2.4. Mikrocontroller ohne Betriebssystem . . . . .                | 34        |

| 2.5. Anforderungen an Echtzeitfähigkeit und Latenz . . . . .      | 35        |

| <b>3. Konzeption des EtherCAT-Feldbus-MainDevices</b>             | <b>37</b> |

| 3.1. Systemanforderungen und Designziele . . . . .                | 37        |

| 3.2. Analyse und Auswahl der Zielhardware . . . . .               | 40        |

| 3.2.1. Analyse der Zielhardware . . . . .                         | 40        |

| 3.2.2. Auswahl und Beschreibung der Zielhardware . . . . .        | 40        |

| 3.3. Architektur des EtherCAT MainDevices . . . . .               | 42        |

| 3.4. Konzeption des Echtzeit-Verarbeitungsmodells . . . . .       | 42        |

| <b>4. Implementierung und Portierung auf den Mikrocontroller</b>  | <b>45</b> |

| 4.1. Hardwarekonfiguration und -anpassung . . . . .               | 46        |

| 4.1.1. Anpassung des STM32-H747-DISCO Evaluation Boards . . . . . | 46        |

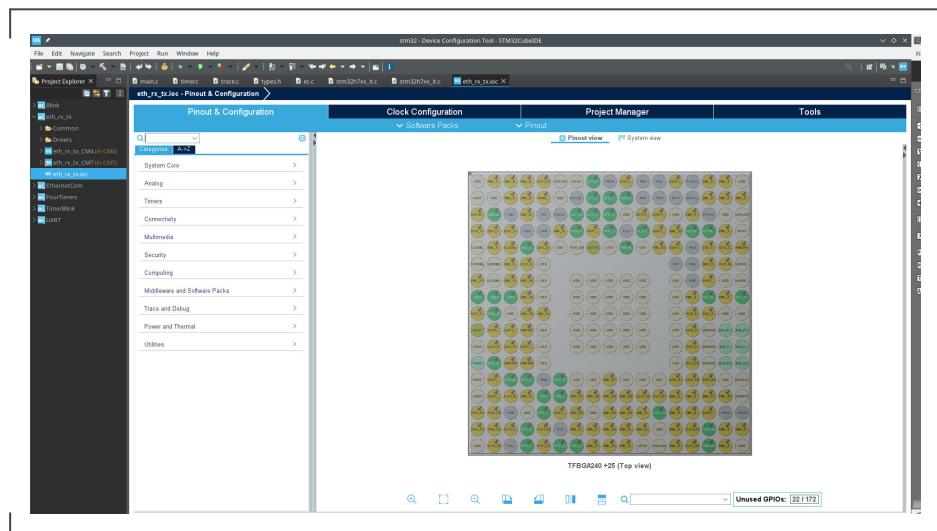

| 4.1.2. Boardkonfiguration . . . . .                               | 47        |

| 4.2. Kommunikationskonfiguration . . . . .                        | 55        |

| 4.2.1. UART-Konfiguration . . . . .                               | 55        |

| 4.2.2. Ethernetkonfiguration . . . . .                            | 56        |

| 4.3. Softwarekonfiguration . . . . .                              | 56        |

| 4.3.1. Interrupts . . . . .                                       | 57        |

| 4.3.2. Ausgabe von UART Nachrichten . . . . .                     | 58        |

| 4.3.3. Senden und Empfangen eines Raw Ethernet Frames . . . . .   | 59        |

| 4.4. Entwicklung der Bibliothekskomponenten . . . . .             | 61        |

| 4.4.1. Critical Sections . . . . .                                | 62        |

| 4.4.2. Debugging Nachrichten . . . . .                            | 64        |

| 4.4.3. EtherCAT Send und Receive Frame . . . . .                  | 65        |

| 4.4.4. Timer ISRs und Zeitfunktionen . . . . .                    | 67        |

| 4.4.5. Semaphoren . . . . .                                       | 67        |

| 4.4.6. Mutexe . . . . .                                           | 68        |

| 4.5. Anpassungen für die Zielhardware . . . . .                   | 69        |

| 4.5.1. Aktivieren der Caches . . . . .                            | 69        |

| 4.5.2. Config File . . . . .                                      | 70        |

| 4.5.3. Abfrage des Ethernet Link Status . . . . .                 | 72        |

|                                                                     |           |

|---------------------------------------------------------------------|-----------|

| 4.5.4. EK1100 LED Second Display . . . . .                          | 73        |

| 4.6. Debugging und Fehlerbehebung . . . . .                         | 74        |

| <b>5. Evaluierung des Echtzeitverhaltens und der Leistung</b>       | <b>75</b> |

| 5.1. Testverfahren und Testaufbau . . . . .                         | 75        |

| 5.1.1. Trace Funktionen aus libosal . . . . .                       | 76        |

| 5.1.2. Testaufbau 1 . . . . .                                       | 79        |

| 5.1.3. Testaufbau 2 . . . . .                                       | 80        |

| 5.2. Messung der Latenz und des Jitters . . . . .                   | 81        |

| 5.2.1. Testaufbau 1 . . . . .                                       | 81        |

| 5.2.2. Testaufbau 2 . . . . .                                       | 83        |

| 5.2.3. Aktivieren der Caches . . . . .                              | 84        |

| 5.3. Interpretation und Diskussion der Ergebnisse . . . . .         | 85        |

| <b>6. Zusammenfassung und Ausblick</b>                              | <b>87</b> |

| 6.1. Zusammenfassung der Arbeit . . . . .                           | 87        |

| 6.2. Ausblick auf zukünftige Arbeiten . . . . .                     | 88        |

| 6.3. Schlussfolgerungen . . . . .                                   | 90        |

| <b>Eigenständigkeitserklärung</b>                                   | <b>i</b>  |

| <b>Quellenverzeichnis</b>                                           | <b>iv</b> |

| <b>Appendix</b>                                                     | <b>i</b>  |

| A. Vollständiger Log-Output EtherCAT StartUP Testaufbau 1 . . . . . | i         |

| B. Vollständiger Log-Output EtherCAT StartUP Testaufbau 2 . . . . . | IX        |

| C. Erstellte Dateien und Ordner . . . . .                           | XVII      |

| D. Excluded Build-Files . . . . .                                   | XIX       |

| E. libethercat config File . . . . .                                | XX        |

| F. libosal config File . . . . .                                    | XXVI      |

| G. analyze.py Skripte . . . . .                                     | XXIX      |

| G.1. analyze_histos.py . . . . .                                    | XXIX      |

| G.2. analyze_boxplot.py . . . . .                                   | XXXIV     |

| H. EtherCAT Wireshark Capture . . . . .                             | XXXVII    |

| I. Programmdateien als .zip . . . . .                               | XXXVIII   |

# Abbildungsverzeichnis

|                                                                                                              |    |

|--------------------------------------------------------------------------------------------------------------|----|

| 1.1. Rollin' Justin Roboter des DLR [DLRb] . . . . .                                                         | 2  |

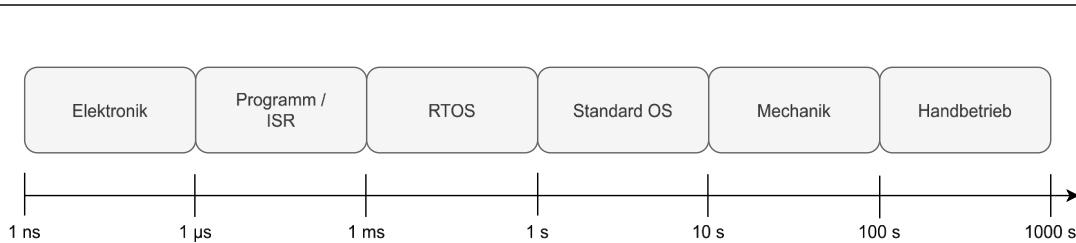

| 2.1. Echtzeitsysteme und ihre Zeitanforderungen [Mäc04] . . . . .                                            | 7  |

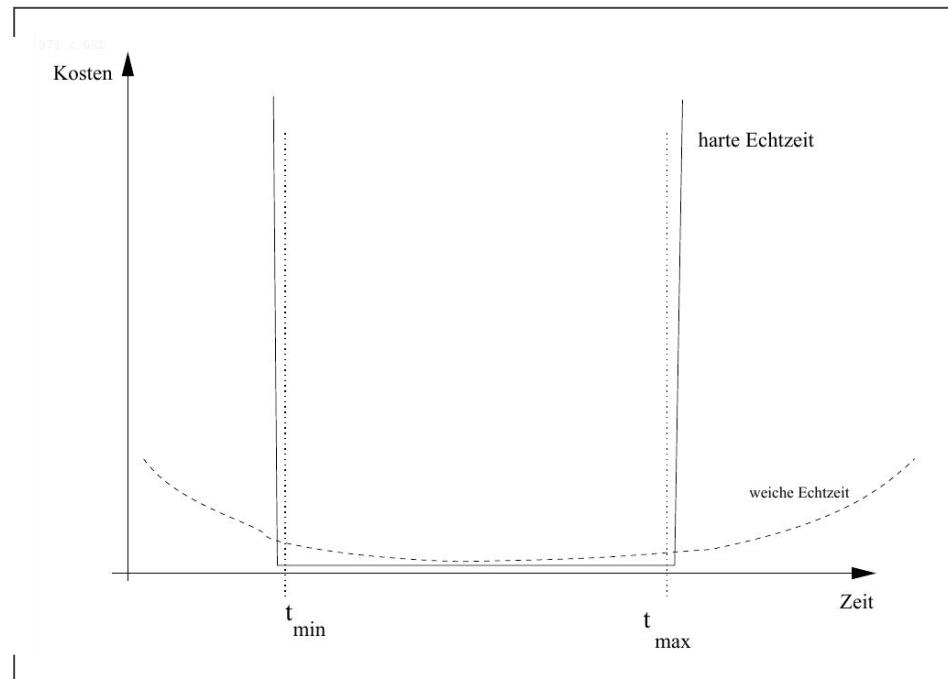

| 2.2. Kostenfunktion harter und weicher Echtzeit [Mäc04] . . . . .                                            | 8  |

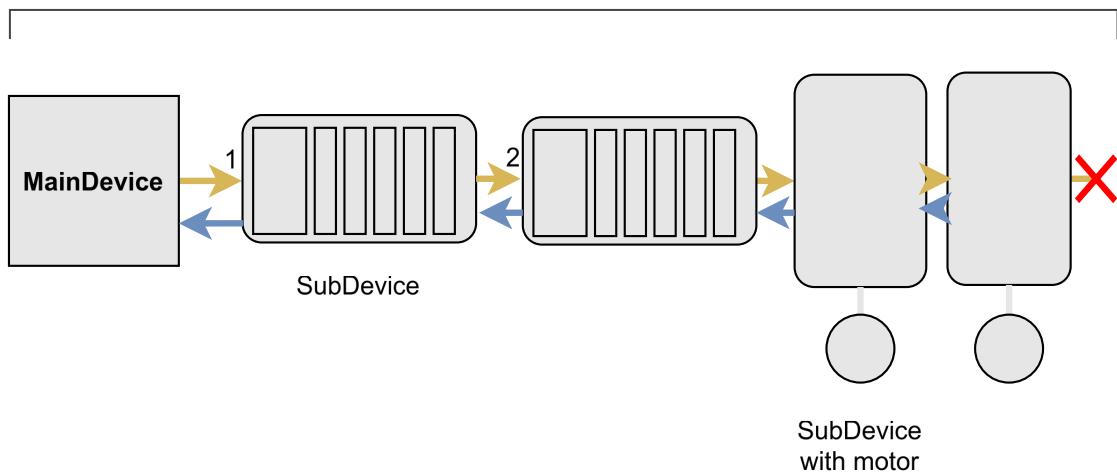

| 2.3. EtherCAT Packet Flow . . . . .                                                                          | 13 |

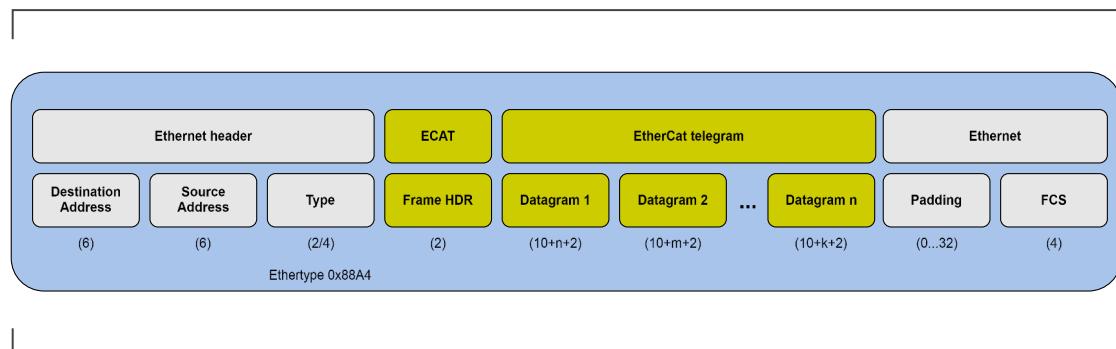

| 2.4. EtherCAT in einem standard Ethernet Frame (nach IEEE 802.3) . . . . .                                   | 14 |

| 2.5. EtherCAT Datagramm . . . . .                                                                            | 14 |

| 2.6. Einfügen von Prozessdaten on-the-fly . . . . .                                                          | 17 |

| 2.7. Flexible Topologie – Bus, Baum oder Stern . . . . .                                                     | 19 |

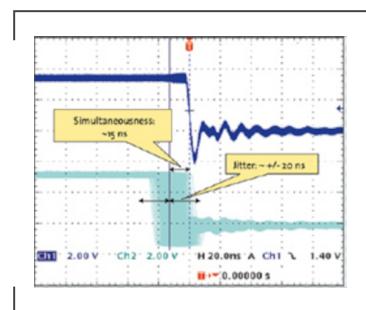

| 2.8. Hardwarebasierte Synchronisierung inkl. Kompensation der Propagation Delays                             | 20 |

| 2.9. Synchronität und Simultanität - zwei distributed Devices mit 300 Nodes und<br>120m Kabellänge . . . . . | 20 |

| 2.10. Billige Kabelredundanz bei Standard EtherCAT SubDevices . . . . .                                      | 23 |

| 2.11. Koexistenz von verschiedenen Kommunikationsprofilen im selben System . . . . .                         | 24 |

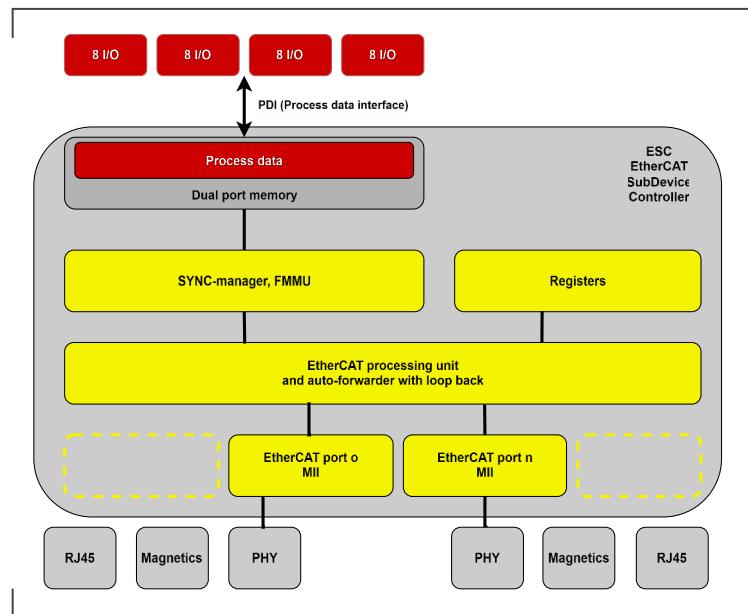

| 2.12. Typische EtherCAT MainDevice Architektur . . . . .                                                     | 27 |

| 2.13. SubDevice Hardware: ESC mit direktem I/O . . . . .                                                     | 28 |

| 2.14. EtherCAT State Machine [Tecc] . . . . .                                                                | 30 |

| 4.1. STM32-H747-DISCO zu lötende Pins . . . . .                                                              | 47 |

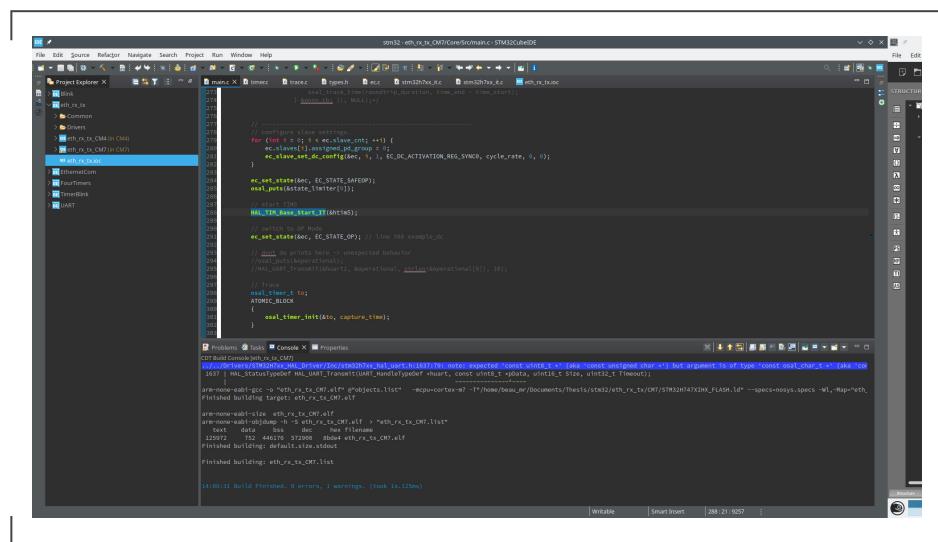

| 4.2. CubeIDE Überblick . . . . .                                                                             | 47 |

| 4.3. CubeIDE .ioc-File Kontext . . . . .                                                                     | 48 |

| 4.4. Zuweisung Timer Module zum CM7-Kontext . . . . .                                                        | 49 |

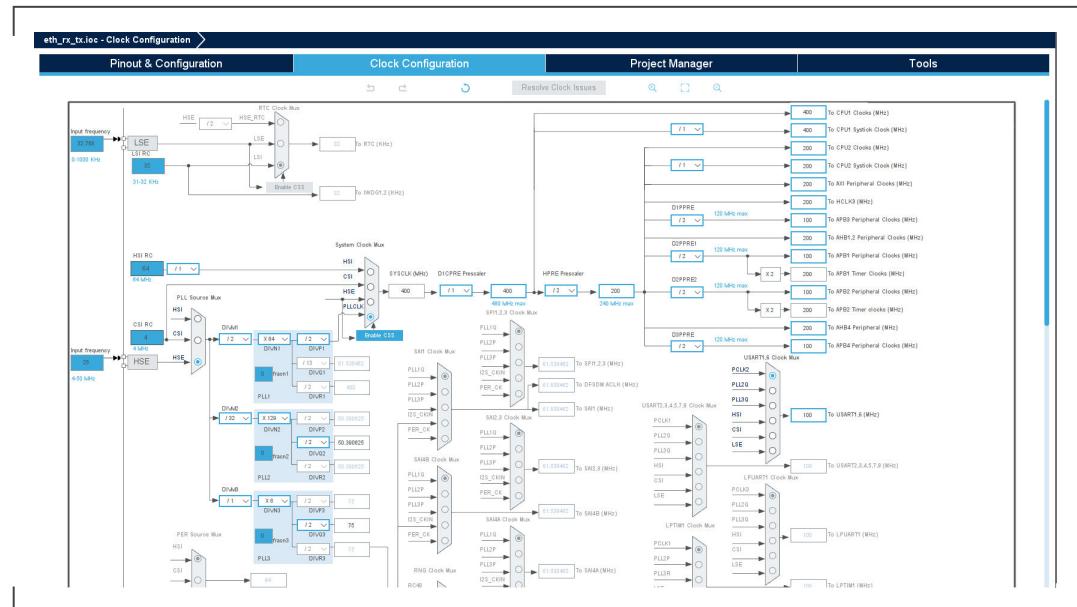

| 4.5. STM32 Clock Configuration Kontext . . . . .                                                             | 50 |

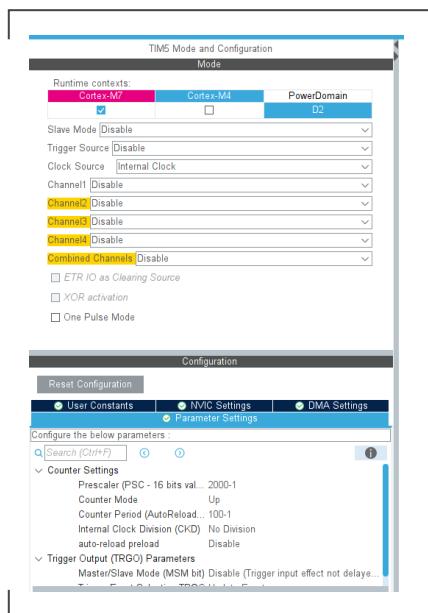

| 4.6. TIM5 Konfiguration im .ioc-File . . . . .                                                               | 53 |

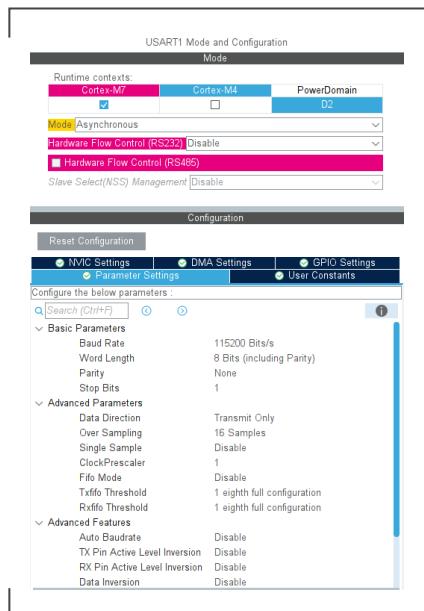

| 4.7. USART1 Konfiguration im .ioc-File . . . . .                                                             | 55 |

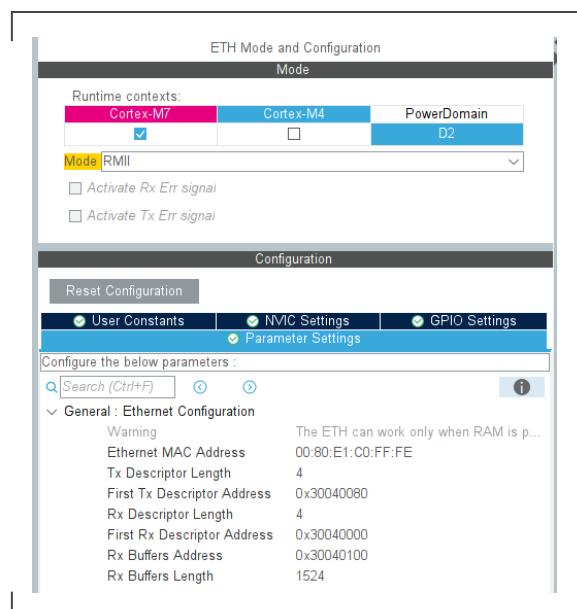

| 4.8. Ethernet Konfiguration im .ioc-File . . . . .                                                           | 56 |

| 4.9. Cache Konfiguration im .ioc-File . . . . .                                                              | 69 |

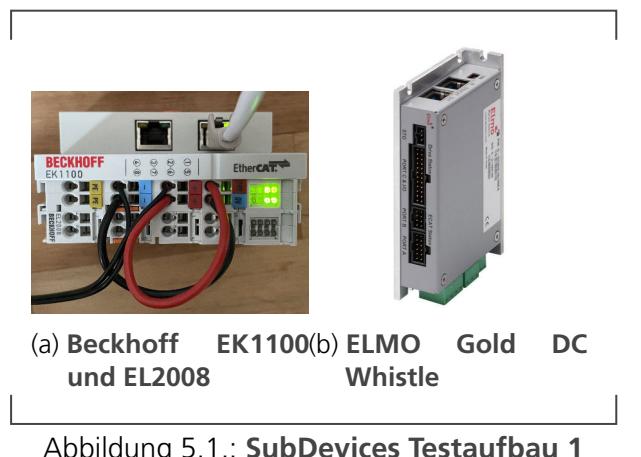

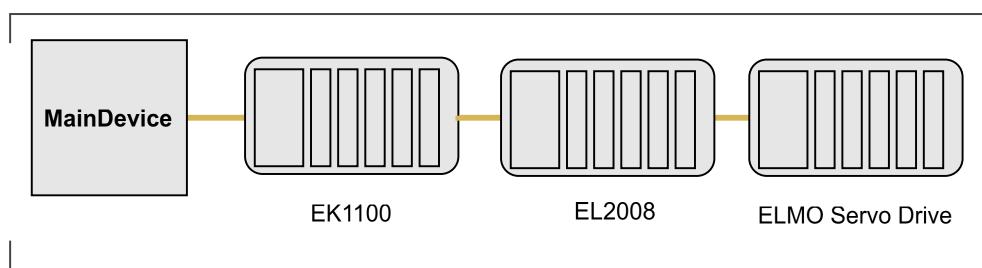

| 5.1. SubDevices Testaufbau 1 . . . . .                                                                       | 79 |

| 5.2. Testaufbau 1: EK1100, EL2008, ELMO Servo Drive . . . . .                                                | 79 |

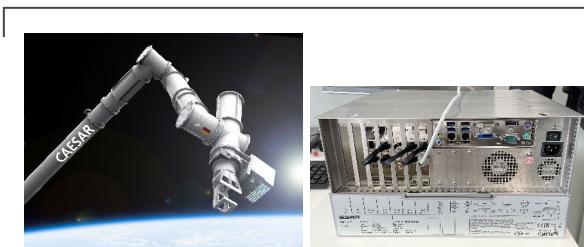

| 5.3. SubDevices Testaufbau 2 . . . . .                                                                       | 80 |

| 5.4. Testaufbau 2: Caesar Simulator mit 4 SubDevices . . . . .                                               | 80 |

---

|                                                                                   |        |

|-----------------------------------------------------------------------------------|--------|

| 5.5. Testaufbau 1: Vergleichsmessungen <code>tx_start</code> . . . . .            | 81     |

| 5.6. Testaufbau 1: Vergleichsmessungen <code>tx_duration</code> . . . . .         | 82     |

| 5.7. Testaufbau 1: Vergleichsmessungen <code>roundtrip_duration</code> . . . . .  | 82     |

| 5.8. Testaufbau 2: Vergleichsmessungen <code>tx_start</code> . . . . .            | 83     |

| 5.9. Testaufbau 2: Vergleichsmessungen <code>tx_duration</code> . . . . .         | 83     |

| 5.10. Testaufbau 2: Vergleichsmessungen <code>roundtrip_duration</code> . . . . . | 84     |

| 1. EtherCAT Wireshark Capture . . . . .                                           | XXXVII |

# Tabellenverzeichnis

|                                                      |    |

|------------------------------------------------------|----|

| 2.1. Eingesetzte Bussysteme . . . . .                | 11 |

| 2.2. EtherCAT Header Fields . . . . .                | 14 |

| 2.3. EtherCAT Datagram Fields . . . . .              | 15 |

| 2.4. EtherCAT Addressing [Tecb] . . . . .            | 16 |

| 2.5. EtherCAT Working Counter [Tecb] . . . . .       | 32 |

| 2.6. EtherCAT Commands [Tecb] . . . . .              | 33 |

| 3.1. Vergleich STM32 und ESP32 . . . . .             | 42 |

| 4.1. STM32-H747-DISC0 zu lötende Pins . . . . .      | 46 |

| 4.2. Funktionen in binary_semaphore.c . . . . .      | 68 |

| 4.3. Funktionen in semaphore.c . . . . .             | 68 |

| 5.1. Erklärung Tracing Variablen . . . . .           | 75 |

| 5.2. Linux MainDevice Spezifikation . . . . .        | 76 |

| 5.3. Testaufbau 1 - Werte der Messungen . . . . .    | 81 |

| 5.4. Testaufbau 2 - Werte der Messungen . . . . .    | 84 |

| 5.5. Laufzeitunterschiede Caches . . . . .           | 84 |

| 5.6. Testaufbau 1 - Prozentualer Vergleich . . . . . | 85 |

| 5.7. Testaufbau 2 - Prozentualer Vergleich . . . . . | 85 |

# Listings

|                                                                         |      |

|-------------------------------------------------------------------------|------|

| 4.1. Flashespeicherkonfiguration . . . . .                              | 54   |

| 4.2. TIM5 Interrupt Handler . . . . .                                   | 57   |

| 4.3. TIM3 Interrupt Handler . . . . .                                   | 58   |

| 4.4. USART Test Code . . . . .                                          | 59   |

| 4.5. Ethernet Send Frame Function . . . . .                             | 60   |

| 4.6. TX Frame Init . . . . .                                            | 61   |

| 4.7. Ethernet Receive DMA Flash Config . . . . .                        | 61   |

| 4.8. Inkludieren der HW-spezifischen Header Files für libosal . . . . . | 62   |

| 4.9. CRITICAL SECTION Declaration . . . . .                             | 62   |

| 4.10. CRITICAL SECTION in der Senderoutine . . . . .                    | 63   |

| 4.11. osal_puts Funktion . . . . .                                      | 64   |

| 4.12. no_verbose_log Funktion in main.c . . . . .                       | 65   |

| 4.13. Deklaration no_verbose_log als ec_log_func in main.c . . . . .    | 65   |

| 4.14. EtherCAT Receive Function in hw_stm32.c . . . . .                 | 66   |

| 4.15. EtherCAT STM32 Hardware Struct . . . . .                          | 66   |

| 4.16. OSAL GET TIME Funktion . . . . .                                  | 67   |

| 4.17. OSAL Mutex Unlock Funktion . . . . .                              | 68   |

| 4.18. Data Cache Invalidation . . . . .                                 | 70   |

| 4.19. Data Cache Flushing . . . . .                                     | 70   |

| 4.20. Config-File . . . . .                                             | 71   |

| 4.21. Ethernet Port LinkStatus Abfrage . . . . .                        | 73   |

| 4.22. EK1100 LED Second Display . . . . .                               | 73   |

| <br>                                                                    |      |

| 5.1. Trace Binary Export . . . . .                                      | 76   |

| 5.2. libosal Tracing in main.c . . . . .                                | 76   |

| 5.3. Group0 Callback Funktion in main.c . . . . .                       | 77   |

| 5.4. Log-Output bzgl. Tracing . . . . .                                 | 78   |

| <br>                                                                    |      |

| 1. EtherCAT Log Output Testaufbau 1 . . . . .                           | I    |

| 2. EtherCAT Log Output Testaufbau 2 . . . . .                           | IX   |

| 3. libethercat Config-File . . . . .                                    | XX   |

| 4. libosal Config-File . . . . .                                        | XXVI |

---

|    |                    |       |

|----|--------------------|-------|

| 5. | analyze_histos.py  | XXIX  |

| 6. | analyze_boxplot.py | XXXIV |

# 1. Einleitung

## 1.1. Motivation

Am Institut für Robotik und Mechatronik (RMC) des Deutschen Zentrums für Luft- und Raumfahrt (DLR) werden Roboter für verschiedene Zwecke gebaut. Diese Roboter sollen bspw. helfen schwere Objekte zu transportieren oder auch herumfliegenden Müll im Erdorbit zu beseitigen und ggf. zu recyceln. Weitere Anwendungsfelder sind u.a. Medizinrobotik, Assistenzrobotik, Produktion der Zukunft und Planetare Explorationsrobotik<sup>1</sup>. Der Roboter *Rollin' Justin*<sup>2</sup> (s. Abbildung 1.1) ist hierbei eine zentrale Plattform für die Forschung im Bereich der Servicerobotik. Er wurde 2008 erstmals der Öffentlichkeit präsentiert und ist insbesondere im Bereich Haushalt und Assistenz von Astronauten im Weltall im Einsatz. Die einzelnen Komponenten des Roboters wie Aktoren oder Sensoren kommunizieren hierbei mittels des Feldbusses **EtherCAT** (Ethernet for Control Automation Technology). Um die Präzision dieser Roboter zu gewährleisten, müssen die anfallenden Daten deterministisch gesendet, empfangen und verarbeitet werden. Durch die schritthalrende Regelung werden natürliche Bewegungen realisiert, da auf Ereignisse reagiert wird. Für diesen Zweck wurden in RMC von Robert Burger zwei OpenSource Bibliotheken geschrieben und auf Github zur Verfügung gestellt. Die Bibliothek `libethercat`<sup>3</sup> implementiert die EtherCAT-Standard spezifischen Abläufe der EtherCAT Technology Group (ETG)<sup>4</sup> und baut auf die Betriebssystem-unabhängige Abstraktionsbibliothek `libosal`<sup>5</sup> auf. Die beiden Bibliotheken sind in C geschrieben. `libosal` zielt darauf ab betriebssystem-unabhängigen Code zu generieren, um eine einfache Portabilität des Codes zwischen verschiedenen Systemen und Architekturen zu gewährleisten. Folgende Betriebssysteme können mit `libosal` bisher verwendet werden:

↗ PikeOS

---

<sup>1</sup>[DLR RM Forschung Anwendungsfelder](#)

<sup>2</sup>[DLR Rollin Justin Website](#)

<sup>3</sup>[GitHub Libethercat](#)

<sup>4</sup>[EtherCAT Website](#)

<sup>5</sup>[GitHub Libosal](#)

- ⇒ POSIX like OS (Unix, Linux und weitere)

- ⇒ VXWorks

- ⇒ Win32

Abbildung 1.1.: **Rollin' Justin** Roboter des DLR [DLRb]

## 1.2. Zielsetzung und Aufgabenstellung

Da die meisten Anwender- als auch Echtzeitbetriebssysteme Nebenläufigkeit in Form von Tasks, Prozessen oder Threads unterstützen, sind diese meist auf einen Scheduler angewiesen, welcher die CPU-Ressourcen effizient den einzelnen Aufgaben zuweist. Dieses Scheduling kann dabei die Anforderungen an die Echtzeitdatenverarbeitung und den Determinismus gefährden. Diese beiden Anforderungen können auch durch andere Software, welche auf den Betriebssystemen und den damit verbundenen Systemen in den Robotern läuft, beeinträchtigt werden. Hierzu zählt beispielweise der Einsatz der Software Simulink.<sup>6</sup> Simulink wird für die Regelungstechnik in den Systemen des DLR genutzt. Aus diesem Grund sollen die beiden Bibliotheken für eine Nutzung auf einem zu definierenden Mikrocontroller erweitert werden, um dedizierte EtherCAT Kommunikation auf dem Mikrocontroller zu realisieren. Dadurch soll die Kommunikation via EtherCAT von der restlichen Software,

<sup>6</sup>[Simulink Website](#)

die für den Betrieb der Roboter benötigt wird, abgekoppelt werden, um Echtzeit und Determinismus in den Systemen weiter zu verbessern. Auf diesem Mikrocontroller soll kein Betriebssystem wie z.B. RTOS (Real-Time Operating System)<sup>7</sup> laufen, weil jedes Betriebssystem auch gewissen Overhead mit sich bringt und die ohnehin schon knappen Ressourcen eines Mikrocontrollers noch mehr verringert. Die Installation eines RTOS macht einen PC nicht direkt echtzeitfähig. Es müssen Mechanismen zu Threads und Hyperthreading erstellt werden und auch jede Hardware noch einmal speziell konfiguriert werden. Dies sind weitere Punkte, die berücksichtigt werden müssen, und einen hohen Grat an Aufwand bedeuten, wenn ein OS wirklich echtzeitfähig gemacht werden soll. Beispielweise muss die Ethernet-Karte für niedrige Latenzen in einen PCIe-Slot verbaut werden und infolgedessen müssen Stromsparmodi von mehreren Hardwaremodulen deaktiviert werden, um Echtzeitanforderungen nicht zu gefährden. Deshalb ist diese Arbeit in erster Linie eine Machbarkeitsstudie, ob es möglich ist, die EtherCAT Kommunikation von den restlichen Softwareapplikation zu trennen und auf einem Mikrocontroller ohne OS zu realisieren.

Hardware-naher Code in C soll direkt auf dem Mikrocontroller implementiert werden, um Einflüsse auf Jitter und Latenz der versendeten Daten zu minimieren. Dadurch soll ein deterministisches System aufgebaut werden. Dafür soll die Funktionsweise der gegenwärtigen Implementierungen zuerst analysiert werden. Anschließend soll ein Konzept zur Realisierung auf der entsprechenden Hardware erstellt und in Betrieb genommen werden. Die Schnittstellen zum Senden und Empfangen von Ethernet-Frames sollen evaluiert und Nebenläufigkeit ohne Betriebssystem oder Scheduler implementiert werden. Daraufhin sollen Messungen zum Echtzeitverhalten und Determinismus erstellt werden. Diese werden mit Messungen der gegenwärtigen Implementierung auf einem Betriebssystem gegenübergestellt. Hierfür müssen Schnittstellen des Mikrocontrollers definiert werden, um zyklische Prozessdaten und azyklischen Daten auszutauschen (s. Abschnitt 2.3). In diesem Abschnitt werden auch die beiden Begriffe *zyklische* und *azyklische* Kommunikation vertieft. Deshalb wird an dieser Stelle auf eine detaillierte Beschreibung verzichtet.

## 1.3. Aufbau der Arbeit

Kapitel 2 beschäftigt sich mit den nötigen Grundlagen für diese Arbeit. Dazu zählen Begriffsdefinitionen zu Echtzeitsystemen und Feldbusystemen. Anschließend wird der EtherCAT Standard erklärt, bevor Vor- und Nachteile eines Mikrocontrollers ohne Betriebssystem erläutert werden. Das Ende des Kapitels zeigt die die nötigen Anforderungen bzgl. Echtzeitfähigkeit und Latenz für diese Arbeit.

Kapitel 3 erläutert die Konzeption des EtherCAT MainDevices. Dazu zählen Systemanforde-

---

<sup>7</sup>[FreeRTOS Website](#)

rungen und Designziele. Anschließend wird Hardware auf diese Anforderungen analysiert und eine begründete Auswahl auf eine Hardware getroffen, die dessen Architektur und Echtzeitanforderungen betreffen.

Kapitel 4 stellt die Portierung der beiden Bibliotheken und Konfiguration der Hardware infolgedessen dar. Außerdem wird auf Tuning der Performance und Debugging eingegangen. Kapitel 5 beschäftigt sich mit zwei Testaufbauten der Implementierung. Dafür werden Messdaten erfasst und mit einer Implementierung eines Linux-MainDevices verglichen und evaluiert.

Das finale Kapitel 6 gibt eine Zusammenfassung dieser Arbeit, Ausblicke in die Zukunft dieser Arbeit und bewertet den Projekterfolg samt Methodik.

## 2. Grundlagen

Dieses Kapitel erläutert die technischen Grundlagen, die für den Betrieb der beiden Bibliotheken auf einem Mikrocontroller ohne Betriebssystem nötig sind. Zunächst wird der Begriff Echtzeit definiert (s. Abschnitt 2.1). Im Anschluss werden Feldbusse und deren Einsatz am DLR erläutert (s. Abschnitt 2.2). Abschnitt 2.3 erklärt den EtherCAT Standard inklusive technischer Parameter und dessen Vorteile. Am Ende des Kapitels werden Vor- und Nachteile eines Mikrocontrollers ohne Betriebssystem genannt (s. Abschnitt 2.4) und anschließend die Anforderungen bzgl. Echtzeit und Latenz erläutert (s. Abschnitt 2.5).

### 2.1. Echtzeitsysteme

Obwohl es keine klare Trennung zwischen Real-Time und Non-Real-Time Systemen gibt, existieren mehrere Faktoren, die bei der Eingrenzung von Real-Time Applikationen helfen [Wil05]. Diese werden in den folgenden Teilabschnitten erklärt. Echtzeit hat nicht alleine etwas mit *Schnelligkeit* zu tun, sondern hängt vielmehr von der *Rechtzeitigkeit* (s. Abschnitt 2.1.2) ab. Diese Rechtzeitigkeit wird durch die *Umgebung* (s. Abschnitt 2.1.8), in der sie stattfindet, definiert. Typischerweise müssen Echtzeitsysteme in Luft- und Raumfahrt binnen weniger Millisekunden reagieren. Anderen Echtzeitsystemen wie bspw. Bahnübergängen genügt eine Reaktionszeit im Sekundenbereich. Für Echtzeitsysteme ist auch von besonderer Bedeutung, dass diese Reaktion unter allen Umständen erfolgt und nicht nur, wenn diese gerade „günstig“ sind [Mäc04].

#### 2.1.1. Scheduling in Echtzeitsystemen

Für Echtzeitbetriebssysteme ist die Zeit der Schlüsselparameter. Normalerweise generieren ein oder mehrere externe Geräte Stimuli und das Echtzeitbetriebssystem muss innerhalb einer bestimmten Zeit reagieren. Beispielsweise muss ein CD-Player die Bits auf einer CD

auslesen und in einer bestimmten Zeit ausgeben. Ist dies nicht der Fall, so klingt die ausgegebene Musik eigenartig. Andere Echtzeitsysteme sind Monitoring von Patienten, Autopiloten im Luftverkehr oder Robotersteuerung in einer automatisierten Fabrik. In all diesen Fällen ist das zu späte Abrufen/Bereitstellen der Daten genauso schlimm, wie wenn diese Daten gar nicht vorhanden wären.

Für alle Echtzeitsysteme ist es deshalb wichtig das Programm in mehrere Prozesse zu unterteilen. Die Eigenschaft dieser Prozesse sollen vorhersagbar und a-priori bekannt sein. Wenn ein externes Event festgestellt wird, ist es die Aufgabe des Schedulers diese Prozesse so zu organisieren, dass alle Deadlines eingehalten werden. Manchmal ist dies nicht möglich, abhängig davon wie viel Zeit diese Events beanspruchen. Diese Events können in *periodische* und *aperiodische* Events unterteilt werden. Beispielsweise kann ein Event  $i$  mit Periode  $P_i$  aus  $m$  periodischen Events, die jeweils  $C_i$  Sekunden an CPU-Zeit benötigen, nur vollständig erfüllt werden, wenn folgende Gleichung gilt:

$$\sum_{k=1}^m \frac{C_i}{P_i} \leq 1 \quad (2.1)$$

Ein Echtzeitsystem, welches diese Gleichung erfüllt, kann mit einem Scheduler realisiert werden. In dieser Gleichung ist eine implizite Annahme, dass das Kontext-Switching über einen so geringen Overhead verfügt, dass es ignoriert werden kann [Tan09].

### 2.1.2. Rechtzeitigkeit

Real-Time Systeme müssen in einem definierten Zeitabschnitt korrekte und vollständige Berechnungen durchführen und deren Ergebnisse zur Verfügung stellen. Tasks müssen zugewiesen und durchgeführt werden, bevor deren *Deadline* (s. Abschnitt 2.1.3) verstreicht. Nachrichten zwischen interagierenden Real-Time Systemen müssen rechtzeitig gesendet und empfangen werden. Die Genauigkeit von Daten hängt nicht nur von deren logischer Korrektheit ab, sondern auch von der Zeit, wann diese erfasst, produziert und pünktlich zur Verfügung gestellt wurden [IEE94]. Steht das Ergebnis eines Prozesses zu spät oder zu früh zur Verfügung, so sind die Daten ungültig, weil sie unbrauchbar sind, obwohl die Daten numerisch korrekt sind. Dies hängt damit zusammen, dass die Daten von einem falschen - einem zu frühen oder zu späten - Zustand des stammen. Deshalb muss die Reaktionszeit größer oder gleich der minimal zulässigen Reaktionszeit liegen. Gleichzeitig muss die Reaktionszeit kleiner oder gleich der maximal zulässigen Reaktionszeit (= Deadline) liegen. Anhand von Abbildung 2.1 ist ersichtlich, dass Echtzeitbetriebssysteme bis zu einer Genauigkeit im Mikrosekunden-Bereich operieren. Echtzeitsysteme im Bereich von Nanosekunden können nur durch Hardware-Lösungen realisiert werden.

Abbildung 2.1.: Echtzeitsysteme und ihre Zeitanforderungen [Mäc04]

Die zeitlichen Bedingungen eines Echtzeitsystems lassen sich in zwei Kategorien unterteilen:

- ↗ Absolute Zeitbedingungen → die Daten müssen zu einem fest definierten Zeitpunkt ausgegeben werden → z.B. 4:20 Uhr

- ↗ Relative Zeitbedingungen → die Daten müssen in einem bestimmten Intervall nach einem Ereignis vorliegen → z.B. 420 s nach Empfang eines Ethernet Frames

### 2.1.3. Deadlines

Deadlines werden in folgende Kategorien unterteilt:

- ↗ Hard → Nichteinhalten der Deadline führt zu katastrophalen Konsequenzen

- ↗ Firm → die meisten aperiodischen Tasks gehören zu dieser Kategorie → Nichteinhalten der Deadline führt dazu, dass

- die Resultate des Tasks nicht mehr nützlich sind

- keine schwerwiegenden Konsequenzen zu erwarten sind

- ↗ Soft → alle restlichen Tasks → der Nutzen der Ergebnisse des Tasks nehmen bei Nichteinhalten der Deadline mit der Zeit ab

Die Einteilung der Tasks in diese Kategorien ist abhängig von der Applikation [IEE94]. Mit Hilfe der Kostenfunktion (s. Abbildung 2.2) kann die Notwendigkeit von Echtzeitschranken

beurteilt werden [Mäc04].

Abbildung 2.2.: Kostenfunktion harter und weicher Echtzeit [Mäc04]

#### 2.1.4. Tasks

Real-Time Applikationen bestehen normalerweise aus mehreren kooperierenden Tasks. Diese Tasks werden in regulären Intervallen aufgerufen/aktiviert und müssen ihre Ausführung innerhalb ihrer Deadlines abgeschlossen haben. Bei jedem Aufruf muss ein Task den Status des Systems determinieren, bestimmte Berechnung ausführen und (falls nötig) Kommandos senden, um den Status des Systems zu ändern oder anzuzeigen. Beispielsweise muss ein Task in einer Flugzeugsteuerung die Ansteuerung des Gaspedals monitoren, Berechnungen zur aktuellen Position durchführen und anschließend die Schubkraft eines Triebwerks durch Anpassung der Kraftstoffeinspritzung ändern.

Dies sind *periodische Tasks*. Sie sind zeitkritisch in dem Sinne, dass das System nicht funktionieren würde, wenn diese Tasks nicht in einer bestimmten Zeit ausgeführt werden. Deshalb ist es für ein Computersystem sehr wichtig, dass die Kriterien bzgl. Deadlines der kritischen Tasks eingehalten werden - unabhängig von den Zuständen anderer Systemkomponenten. *Aperiodische Tasks* werden ausgeführt, wenn bestimmte Events eintreten. Beispielsweise

wird ein Systemkonfigurations-Task nur bei Auftreten eines Fehlers aktiviert. Da diese Events nicht in regulären Intervallen auftreten, werden die korrespondierenden Tasks auch nicht regelmäßig ausgeführt. Wenn das Event zeitkritisch ist, hat der zugehörige aperiodische Task eine Deadline. Wenn das Event nicht zeitkritisch ist, dann hat der Task keine Deadline. Er muss so schnell wie möglich abgearbeitet werden ohne dabei die Deadlines anderer Tasks zu beeinträchtigen [IEE94].

### 2.1.5. Gleichzeitigkeit und Auslastung

Echtzeitsysteme stehen auch vor der Herausforderung, dass mehrere Aufgaben gleichzeitig auftreten und bearbeitet werden müssen. Auch dann müssen diese Aufgaben pünktlich und korrekt erledigt werden. Um dies zu gewährleisten, können bspw. mehrere Subsysteme diese Ereignisse verarbeiten. Dazu können die auszuführenden Aufgaben auf mehrere Tasks verteilt werden, die sich unterbrechen können. Dies stellt eine weitere Herausforderung bei der Konzeption und Realisierung von Echtzeitsystemen dar. Andererseits kann das gleichzeitige Eintreten von Aufgaben auch durch den Einsatz von sehr schnellen, verarbeitenden Systemen sichergestellt werden, da diese Systeme die Daten sehr viel schneller verarbeiten als neue Ereignisse auftreten. Wichtig ist hierbei, dass die Gesamtkapazität zur Erledigung der einzelnen Prozesse in Summe nicht überschritten wird [Mäc04].

### 2.1.6. Determinismus

Die Berechenbarkeit des Zeitverhaltens in einem System nennt sich zeitlicher Determinismus. Nur wenn sich ein System zeitlich-deterministisch verhält, kann Echtzeitverhalten garantiert werden [Mäc04]. Bereits beim Design des Systems sollte es möglich sein, dass alle Zeitvorgaben der Anwendungen erfüllt werden, solange bestimmte Systemmaßnahmen vorliegen. Deshalb müssen die Einschränkungen aller Tasks a-priori bekannt sein. Dazu zählen die Anzahl, Ausführungszeiten und Ressourcenbedingungen aller Tasks. Zeitliche Veränderungen innerhalb der Systemumgebung können das Verhalten des Systems maßgeblich beeinflussen. Garantien zu Deadlines sind nur möglich, wenn die Ausführungs- und Ankunftszeit von Tasks a-priori bekannt sind.

Während des Systemdesigns liegen meist nicht alle Informationen über diese Anforderungen vor. Deshalb werden oft Annahmen bzgl. des Worst-Case genutzt, um voraussagen zu können, ob die Echtzeit eingehalten werden kann. Die Daten des Worst-Case stammen aus Simulationen, Tests und anderen Vorgängen. Die tatsächlichen Daten der Worst-Cases können die Annahmen überschreiten. Da es keine anderen Alternativen gibt, muss zuerst mit den Annahmen des Worst-Cases gearbeitet werden [IEE94]. Dies stellt einen Gegensatz

zu vielen Modellen in der Informatik dar, da diese für den Durchschnittsfall optimiert sind. Echtzeitsysteme müssen gegenüber des Worst-Cases optimiert werden. Dafür wird oft davon ausgegangen, dass alle Ereignisse zum selben Zeitpunkt eintreten und ihre maximale Ausführungszeit in Anspruch nehmen [Mäc04].

### 2.1.7. Zuverlässigkeit-/Performancebedingungen

Ein Task muss bestimmte Zuverlässigkeit-, Verfügbarkeits und/oder Performancebedingungen erfüllen. Zuverlässigkeit ist extrem wichtig. Der Ausfall eines Real-Time Systems könnte zu einem ökonomischen Desaster oder dem Verlust von Menschenleben führen [IEE94]. Die Zuverlässigkeit eines Systems hängt stark mit dessen *Hard Deadlines* ab. Beispiele hierfür sind Systeme in Flugzeugen, Kraftwagen oder auch Kraftwerken [Mäc04].

### 2.1.8. Umgebung

Die Umgebung, in welcher ein Computer arbeitet, ist eine aktive Komponente jedes Real-Time Systems. Beispielsweise ist der Einsatz von On-Board Computern in einem Drive-by-Wire System nutzlos ohne das Auto selbst [IEE94]. Die Umgebung wird auch *externes System* genannt. Dieses externe System gibt die relevanten Bedingungen für das Echtzeitsystem vor [Mäc04].

## 2.2. Feldbusse

Feldbusse sind Netzwerke, um Geräte wie Sensoren, Aktuatoren, PLCs (Programmable Logic Controllers), Regulatoren oder auch Man-Machine-Interfaces miteinander zu verbinden, damit diese Daten miteinander austauschen können. Die verschiedenen Feldbussysteme adressieren alle ähnliche Probleme, unterscheiden sich jedoch leicht in Art und Weise. Sie hängen primär von folgenden Punkten ab:

- ↗ Anforderungen der End-User in verschiedenen Branchen

- ↗ Anzahl und Vielfalt der angeschlossenen Hosts

- ↗ technische Möglichkeiten zur Zeit der Entwicklung

Abhängig davon entwickelten Unternehmen ihre proprietären Lösungen und standardisierten diese [Tho05]. Zu einem Feldbussystem gehören spezifische Hardwarekomponenten wie Kabel und Konnektoren. Zusätzlich müssen für jeden Feldbus Kommunikationsprotokolle definiert sein. Gängige Feldbussysteme sind:

- ↗ Profibus / Profinet<sup>1</sup>

- ↗ Modbus<sup>2</sup>

- ↗ DeviceNet<sup>3</sup>

- ↗ CAN<sup>4</sup>

- ↗ SERCOS-III<sup>5</sup>

- ↗ EtherCAT (s. Abschnitt 2.3)

Die Entwicklungen am DLR sind heterogene Systeme bzgl. der Kommunikationsbusse. Folgende Busse sind im Einsatz:

Tabelle 2.1.: **Eingesetzte Bussysteme**

| Bussystem | Einsatz                                                |

|-----------|--------------------------------------------------------|

| Ethernet  | RT, non-RT, Kameras                                    |

| SERCOS-II | LWR Joints                                             |

| SpaceWire | HAND-II, HaSy/David, MiroSurge                         |

| EtherCAT  | Beckhoff Terminals, ELMO Boxes, Digi-I/O               |

| CAN       | Heinzmann Wheels, Schunk Grippers/Pan-Tilt             |

| SSI       | Positionenkoder                                        |

| USB       | Asus Xtion, XSense IMU's, verschiedene Mikrocontroller |

| Serial    | Medical Hands, Dynamixel Servis, DLR FTS-78            |

<sup>1</sup>[Profibus Website](#)

<sup>2</sup>[Modbus Website](#)

<sup>3</sup>[DeviceNet Einführung von Beckhoff](#)

<sup>4</sup>[Can knowledge in CiA \(CAN in Automation\)](#)

<sup>5</sup>[Sercos III Erklärung der Sercos](#)

## 2.3. EtherCAT

EtherCAT steht für ***Ethernet for Control Automation Technology***. Es ist eine Echtzeit-Industrie-Ethernet-Technologie, die ursprünglich von Beckhoff Automation<sup>6</sup> entwickelt wurde und im IEC (International Electrotechnical Commission) Standard IEC61158 veröffentlicht wurde. Sie ist geeignet für Hard- und Soft-Real-Time-Anforderungen in der Automationstechnik, Tests, Messungen und andere Anwendungen. Während der Entwicklung lag der Fokus vor allem auf kurzen Zykluszeiten ( $\leq 100\mu\text{s}$ ), niedrigem Jitter für akkurate Synchronisation ( $\leq 1\mu\text{s}$ ) und niedrigen Hardwarekosten.

EtherCAT wurde im April 2003 vorgestellt und die EtherCAT Technology Group (ETG) wurde im November 2003 gegründet. In der Zwischenzeit hat sich die ETG zur weltweit größten Organisation für Industrial Ethernet und Feldbusse entwickelt. Sie vereint viele Hersteller und Nutzer, welche zum Fortschritt der EtherCAT Technologie in technischen Arbeitsgruppen zusammenarbeiten [Eth].

### 2.3.1. Funktionsprinzip

Das EtherCAT MainDevice (veraltet: Master) sendet ein Telegram, das durch alle am Bus angeschlossenen Nodes geht. Jedes SubDevice (veraltet: Slave) liest die Daten, welche für sie bestimmt sind „on-the-fly“ aus dem Telegram aus und fügt eigene Daten an diese Stelle im Frame ein. Der Frame verzögert sich nur durch Hardware Propagation Delays. Das letzte Device im Bus erkennt einen offenen (nicht angeschlossenen) Port und sendet die Nachricht via Full-Duplex zurück an das MainDevice. Die SubDevices nutzen einen EtherCAT SubDevice Controller (ESC). Dies ermöglicht, dass die Daten on-the-fly und in Hardware verarbeitet werden können, um die Network-Performance vorhersagbar und unabhängig von der individuellen SubDevice Implementierung zu machen [Eth]. Dies ähnelt dem *Cut-Through Forwarding* in geswitchten Netzwerken. Die SubDevices verfügen dafür über spezielle ASICs (Anwendungsspezifische integrierte Schaltung), damit die Frames mit einem Delay im Nanosekundenbereich versendet werden können.

Die maximale, effektive Datenrate erhöht sich auf über 90%. Durch das Nutzen des Full-Duplex Features ist die theoretisch erreichbare, effektive Datenrate höher als 100 MBit/s ( $> 90\% \times 2 \times 100 \text{ MBit/s}$ ).

Das EtherCAT MainDevice ist das einzige Gerät innerhalb eines Segments, das aktiv einen EtherCAT Frame versenden darf; die restlichen Nodes leiten die Frames lediglich im Downstream weiter. Dieses Konzept verhindert unvorhersagbare Delays und garantiert Echtzeit-Fähigkeit.

---

<sup>6</sup>Beckhoff Website

Das MainDevice nutzt einen Standard Ethernet Media Access Controller (MAC) ohne zusätzlichen Kommunikationsprozessor. Dies ermöglicht, dass das MainDevice auf jeder Hardwareplattform implementiert werden kann, das über einen Ethernet Port verfügt. Dies ist unabhängig davon, ob ein Echtzeit-Betriebssystem (RTOS) oder welche Anwendungssoftware genutzt wird.

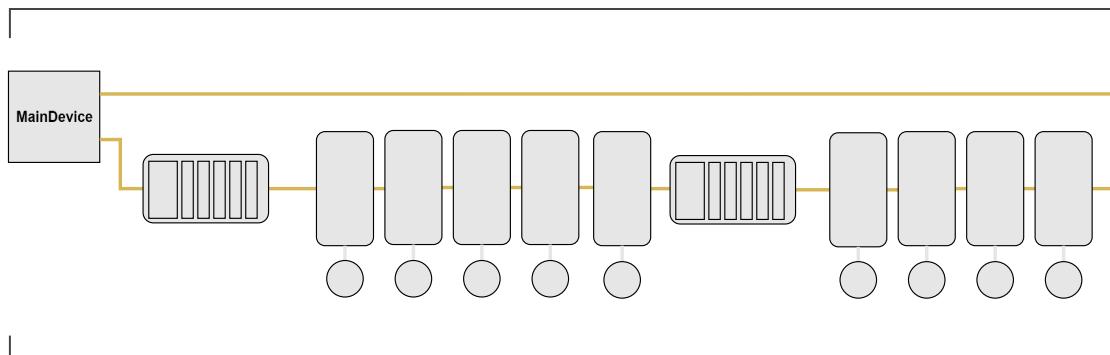

### 2.3.2. EtherCAT Packet Flow

EtherCAT Devices verfügen üblicherweise über zwei Ports, können aber auch mehr haben. Das MainDevice hat im Normalfall nur einen Port in Benutzung, an den das erste SubDevice angeschlossen ist (s. Abbildung 2.3). Das MainDevice sendet über seine TX-Leitung den EtherCAT Frame an den ersten Port des angeschlossenen SubDevices. Das SubDevice empfängt den Frame auf der RX-Leitung des Ports. Dieses SubDevice verarbeitet die Daten und sendet diese über die TX-Leitung des zweiten Ports weiter (= Downstream ≡ gelber Pfeil in der Skizze). Wenn ein SubDevice erkennt, dass nur ein Port in Benutzung ist, sendet es die Daten über die TX-Leitung seines Eingangsports wieder zurück an das vorherige Device (= Upstream ≡ blauer Pfeil in der Skizze). Dies geschieht solange bis der Frame am MainDevice über dessen RX-Leitung wieder empfangen wird. Sollte der zweite Port des letzten SubDevices in der Kette direkt mit dem zweiten Port des MainDevices verbunden sein, werden die Daten über diese Ports in einer Ringstruktur gesendet (s. Abbildung 2.10).

Abbildung 2.3.: EtherCAT Packet Flow

### 2.3.3. Das EtherCAT Protokoll

EtherCATbettet seinen Payload in einen Standard Ethernet Frame ein (s. Abbildung 2.4). Der Ethertype ist hierbei 0x88A4. Da EtherCAT für kurze, zyklische Prozessdaten optimiert wurde, ist das Nutzen von Protokollstacks wie TCP/IP oder UDP/IP obsolet [Eth].

Abbildung 2.4.: EtherCAT in einem standard Ethernet Frame (nach IEEE 802.3)

Der 2-Byte-lange EtherCAT Header ist in drei Felder (vgl. Tabelle 2.2) unterteilt. Ein EtherCAT

Tabelle 2.2.: EtherCAT Header Fields

| Feld     | Länge  | Wert/Beschreibung                                            |

|----------|--------|--------------------------------------------------------------|

| Length   | 11 Bit | Länge des EtherCAT Datagrams ohne FCS                        |

| Reserved | 1 Bit  | Reserviert, 0                                                |

| Type     | 4 Bit  | Protokoll-Typ, SubDevices unterstützen nur <i>Type = 0x1</i> |

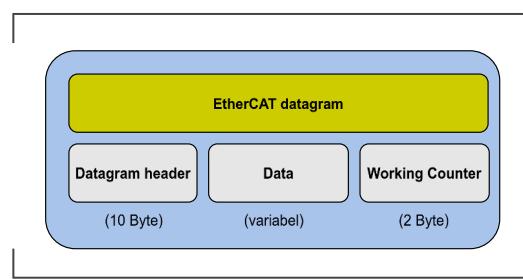

Telegramm kann aus bis zu 15 EtherCAT Datagrammen bestehen. Jedes Datagramm in einem EtherCAT Telegramm besteht aus einem Datagramm Header, zugehörigen Daten und dem Working Counter (s. Abbildung 2.5).

Abbildung 2.5.: EtherCAT Datagramm

Tabelle 2.3.: EtherCAT Datagramm Fields

| Feld    | Länge   | Wert/Beschreibung                                                                                                                                           |

|---------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cmd     | 1 Byte  | EtherCAT Kommando-Typ                                                                                                                                       |

| Idx     | 1 Byte  | numerische Kennung für die Identifizierung des MainDevices von Duplikaten oder verlorengegangenen Datagrammen; SubDevices sollten diesen Index nicht ändern |

| Address | 4 Byte  | Adresse: Auto-Inkrement, Configured Station oder Logische Adresse                                                                                           |

| Len     | 11 Bit  | Länge der Datagramm-Daten                                                                                                                                   |

| R       | 3 Bit   | Reserviert, 0                                                                                                                                               |

| C       | 1 Bit   | Umlaufender Frame:<br>0 = Frame läuft nicht um<br>1 = Frame ist einmal umgelaufen                                                                           |

| M       | 1 Bit   | Mehrere Datagramme:<br>0 = Letztes Datagramm<br>1 = mindestens 1 weiteres folgt noch                                                                        |

| IRQ     | 1 WORD  | Ereignis-Abfrage-Register<br>Kombination aller SubDevices mit logischen OR                                                                                  |

| Data    | n Bytes | zu lesende/schreibende Daten                                                                                                                                |

| WKC     | WORD    | Working Counter                                                                                                                                             |

Der Datagramm Header ist in zehn Felder unterteilt, welche wie in Tabelle 2.3 spezifiziert sind.

Das 4-Byte-lange Adressfeld (vgl. Tabelle 2.4) kann auf mehrere Arten genutzt werden:

- ↗ Position Addressing → nur für Startup des EtherCAT Systems und um neu hinzugefügte SubDevices zu erkennen; jedes SubDevice erhöht diese Adresse um 1

- ↗ Node Addressing → Registerzugriff auf einzelne, schon identifizierte Geräte

- ↗ Logical Addressing → bitweise Zuordnung von Daten in einem 32-bit breiten, virtuellen Adressraum

- ↗ Broadcast Addressing → Initialisierung aller SubDevices

Je nachdem welche Adressierungsart genutzt wird, werden die 4 Byte anders aufgeteilt

und genutzt (s. Tabelle 2.4) [Tecb]. Um Ethernet IT-Kommunikation zwischen den Nodes

Tabelle 2.4.: EtherCAT Addressing [Tecb]

| Modus                                           | Feld     | Länge | Wert/Beschreibung                                                                                                       |

|-------------------------------------------------|----------|-------|-------------------------------------------------------------------------------------------------------------------------|

| Position Address ODER<br>Auto Increment Address | Position | WORD  | jedes SubDevices erhöht den Wert<br>SubDevice wird angesprochen,<br>wenn Position = 0                                   |

|                                                 | Offset   | WORD  | Lokale Register- oder Speicheradresse des ESCs                                                                          |

| Node Address ODER<br>Configured Station Address | Address  | WORD  | SubDevice wird adressiert,<br>wenn Address = Configured Station Address<br>ODER Address = Configured Station Alias      |

|                                                 | Offset   | WORD  | Lokale Register- oder Speicheradresse des ESCs                                                                          |

| Broadcast                                       | Position | WORD  | SubDevice erhöht den Wert                                                                                               |

|                                                 | Offset   | WORD  | Lokale Register- oder Speicheradresse des ESCs                                                                          |

| Logical Address                                 | Address  | DWORD | Logische Adresse (konfiguriert von FMMUs)<br>SubDevice wird adressiert,<br>wenn FMMU Konfiguration = Wert im Adressfeld |

zu gewährleisten, können TCP/IP Verbindungen optional durch einen Mailbox Channel getunnelt werden, ohne dabei den Echtzeit-Datenaustausch zu gefährden. Während des Startvorgangs des Busses konfiguriert und mappt das MainDevice die Prozessdaten auf den SubDevices. Verschiedene Mengen an Daten (1 Bit bis zu mehreren Kilobytes) können pro SubDevice ausgetauscht werden.

Der EtherCAT Frame beinhaltet ein oder mehrere Datagramme. Der Datagram Header gibt an, welche Art des Zugriffs das MainDevice gerne ausführen würde:

- Read, Write, Read-Write

- Zugriff auf ein bestimmtes SubDevice durch direkte Adressierung oder Zugriff auf mehrere SubDevices durch logische bzw. implizite Adressierung

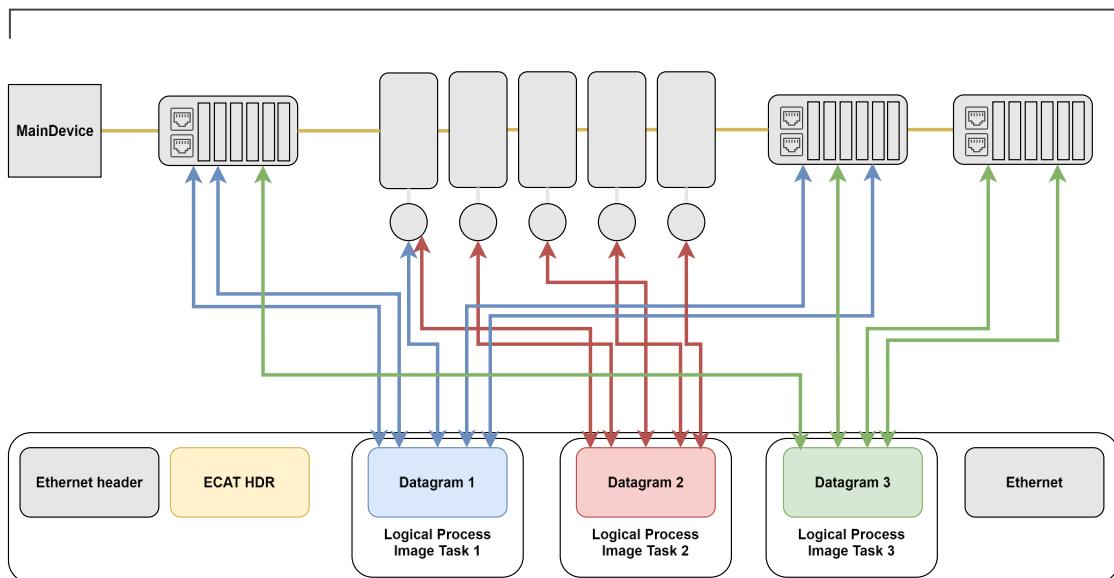

Logische Adressierung wird für den zyklischen Austausch von Prozessdaten verwendet. Jedes Datagramm adressiert einen spezifischen Teil des Prozessabbildes im EtherCAT Segment. Dafür sind 4 GByte im Adressraum vorhanden. Während des Hochfahrens des Netzwerks wird jedem SubDevice eine oder mehrere Adressen in diesem globalem Adressraum zugewiesen. Wenn mehrere SubDevices im selben Adressraum liegen, können sie alle mit einem einzigen Datagramm adressiert werden. Da das Datagram alle Daten beinhaltet, die für den Zugriff benötigt werden, kann das MainDevice entscheiden, wann und auf welche Daten es zugreift. Beispielsweise kann das MainDevice kurze Zykluszeiten nutzen, um die Daten in den Speichern aktualisieren, und längere Zykluszeiten, um die I/O Daten zu samplen. Deshalb ist eine fixe Prozessdatenstruktur nicht notwendig. Dies entlastet das MainDevice im Vergleich zu konventionellen Feldbussen. In konventionellen Feldbussen müssen die Daten der Nodes individuell ausgelesen, mit Hilfe eines Prozesscontrollers sortiert und in

den Speicher kopiert werden.

Mit EtherCAT muss das MainDevice nur einen einzelnen EtherCAT Frame mit neuen Output-Daten initialisieren und den Frame via Direct Memory Access (DMA) an den MAC-Controller senden. Wenn ein Frame mit neuen Input-Daten am MAC-Controller empfangen wird, kopiert das MainDevice diese Daten via DMA in den Speicher des Geräts. Dies geschieht ohne aktive Nutzung der CPU. Ergänzend zu den zyklischen Daten können Datagramme benutzt werden, um asynchrone oder event-basierte Kommunikation zu realisieren.

Zusätzlich zur logischen Adressierung kann das MainDevice die SubDevices durch die

Abbildung 2.6.: Einfügen von Prozessdaten on-the-fly

Position im Netzwerk adressieren. Diese Methode wird während des Network-Boots verwendet, um die Netzwerktopologie zu bestimmen und diese mit der geplanten Topologie zu vergleichen.

Nachdem die Netzwerkkonfiguration überprüft wurde, kann das MainDevice jedem Node eine konfigurierte Node-Adresse zuweisen und durch diese mit den Nodes kommunizieren. Dies ermöglicht gezielten Zugriff auf Geräte, auch wenn sich die Netzwerktopologie im laufenden Betrieb verändert, was durch Hot Connect Groups geschehen kann. Es gibt zwei verschiedene Ansätze für SubDevice-to-SubDevice-Kommunikation. Ein SubDevice kann Daten direkt an andere SubDevices senden, die sich im Downstream-Pfad des Netzes befinden. Da EtherCAT Frames nur in Vorwärtsrichtung verarbeitet werden können, ist dieser Ansatz von der Netzwerktopologie abhängig und nur für ein unveränderliches Machine-Design geeignet (z.B. für Drucker oder Verpackungsanlagen).

Im Gegensatz dazu findet die freie SubDevice-to-SubDevice-Kommunikation über das MainDevice statt. Diese Kommunikation benötigt zwei Buszyklen (nicht zwangsweise zwei Kontrollzyklen). Aufgrund der hervorragenden Performance von EtherCAT ist diese Art der SubDevice-to-SubDevice-Kommunikation immer noch schneller als andere Kommunikationstechniken [Eth].

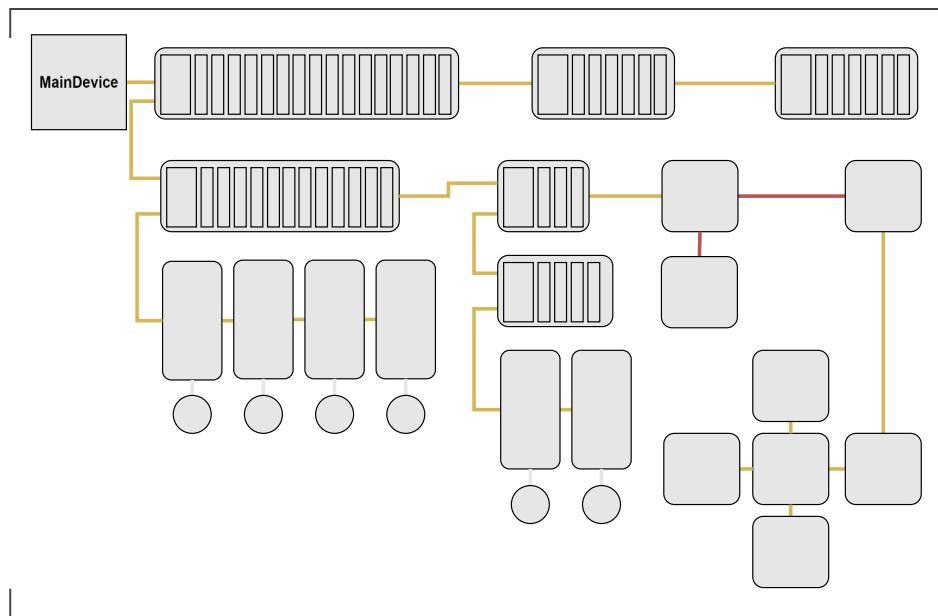

### 2.3.4. Flexible Topologie

EtherCAT unterstützt fast alle Topologien wie bspw. Bus, Baum, Stern oder auch Daisy-Chain. EtherCAT baut eine reine Bustopologie mit hunderten von Nodes auf. Die Umsetzung erfolgt ohne die standardmäßigen Limitationen, die auftreten, wenn Switches oder Hubs kaskadiert werden.

Beim Verkabeln des Netzes ist eine Kombination aus Anschlussleitungen hilfreich: die Ports, welche für die Anschlussleitungen benötigt werden, sind direkt in viele I/O Module integriert. Deshalb werden keine zusätzlichen Switches oder andere aktive Hardware benötigt. Die für Ethernet standardmäßige Sterntopologie kann so natürlich genutzt werden.

Modulare Maschinen oder Tool Changers setzen Voraus, dass Netzwerksegmente oder individuelle Nodes während des Betriebs angeschlossen oder abgetrennt werden. EtherCAT SubDevice-Controllers haben die Voraussetzungen dieses Hot-Connect-Features' standardmäßig implementiert. Wenn ein Nachbarnode vom Bus getrennt wird, wird der Port automatisch geschlossen, damit der Rest des Netzes weiterhin ohne Interferenzen funktionieren kann. Kurze Detektionszeiten von < 15µs garantieren eine reibungslose Anpassung (= ChangeOver) der Topologie.

EtherCAT bietet eine große Flexibilität, was die Art der verwendeten Kabel betrifft. Jedes Segment kann mit genau den Kabeln bestückt werden, die dessen Anforderungen am besten erfüllt. Billige Industrial-Ethernet-Kabel können im 100BASE-TX Mode zwischen zwei Nodes genutzt werden, die sich bis zu 100m entfernt befinden. Mit der Protokoll Erweiterung *EtherCAT P* können sowohl Daten als auch Strom über lediglich ein Kabel übertragen werden. Dadurch können Geräte wie Sensoren in einer Bustopologie angeschlossen werden. Glasfaseroptiken und deren Kommunikationsstandard wie z.B. 100BASE-FX können genutzt werden, um Geräte zu verbinden, die sich mehr als 100m voneinander entfernt befinden. Die vollständige Breite von Ethernet Verkabelung ist deshalb für EtherCAT verfügbar.

Bis zu 65535 ( $2^{16}$ ) Geräte können an einem EtherCAT Segment angeschlossen werden. Deshalb ist die Erweiterung des Netzes virtuell unlimitiert und modulare Geräte wie „sliced“ I/O-Stationen können so designt werden, dass jedes Modul wie eine unabhängige EtherCAT Node operiert. Dadurch entfällt der lokale Erweiterungsbus. Durch die hohe Performance von EtherCAT wird jedes Modul direkt und ohne jegliche Delays erreicht, da es kein Gateway im Buskoppler oder in der Kopfstation gibt [Eth].

Abbildung 2.7.: Flexible Topologie – Bus, Baum oder Stern

### 2.3.5. Distributed Clocks für High-Precision Synchronisierung

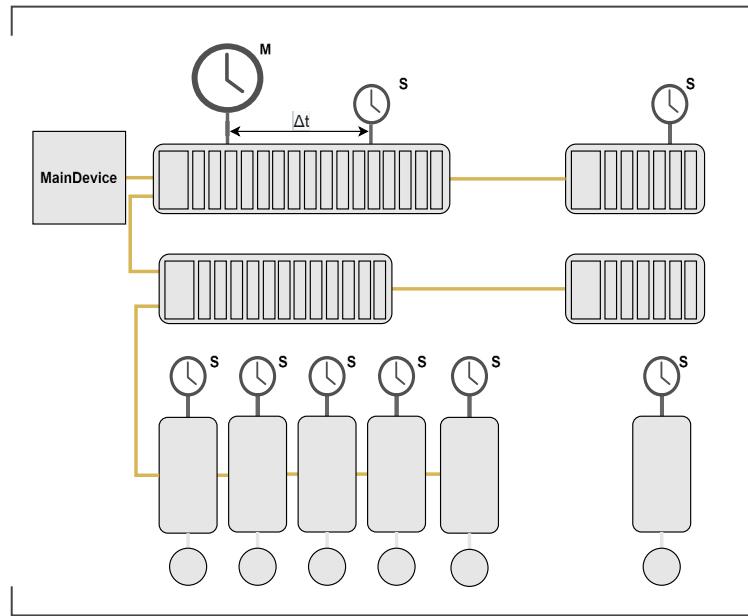

Insbesondere in Anwendungen mit räumlich verteilten Prozessen, welche simultane Ausführung benötigen, ist Synchronisierung sehr wichtig; beispielweise in Anwendungen, welche mehrere Servoaxen ansprechen, um koordinierte Bewegungen gleichzeitig auszuführen. Die Qualität von vollständig synchroner Kommunikation leidet direkt unter Kommunikationsfehlern. Im Gegensatz dazu haben Distributed Synchronized Clocks einen hohen Grad an Fehlertoleranz bzgl. des Jitters in einem Kommunikationssystem. Deshalb erfolgt die Synchronisierung der Nodes in EtherCAT durch Distributed Clocks (DC). Die Kalibrierung der Clocks in den Nodes ist komplett hardwarebasiert. Die Zeit des ersten DC SubDevice wird zyklisch an alle anderen Geräte im System weitergegeben. Mit diesem Mechanismus können die SubDevice Clocks präzise an diese Referenz-Clock angepasst werden. Der daraus resultierende Jitter ist  $<1\mu\text{s}$ .

Da diese Referenz-Clock leicht verzögert an den SubDevices empfangen wird, muss das Propagation Delay für jedes SubDevice gemessen und kompensiert werden. Dies stellt Synchronität und Simultanität sicher. Dieses Delay wird während des Netzwerkstarts gemessen. Zusätzlich kann dies während laufenden Betriebs stattfinden, um sicherzustellen, dass die Clocks simultan innerhalb von  $1\mu\text{s}$  zueinander laufen. Wenn alle Nodes die selbe Information über die Zeit haben, können sie ihre Output-Signale simultan setzen und einen hoch präzisen Timestamp an ihre Input-Signale anhängen. In Motion Control Anwendungen ist

Abbildung 2.8.: **Hardwarebasierte Synchronisierung inkl. Kompensation der Propagation Delays**

Abbildung 2.9.: **Synchronität und Simultanität - zwei distributed Devices mit 300 Nodes und 120m Kabellänge**

die Zyklusgenauigkeit zusammen mit Synchronität und Simultanität sehr wichtig. In solchen Anwendungen wird die Geschwindigkeit anhand der gemessenen Position bestimmt. Deshalb ist es wichtig, dass die Ortsbestimmung äquidistant (z.B. genaue Zyklen) vorgenommen wird. Kleine Ungenauigkeiten in der Ortsbestimmung können zu größeren Ungenauigkeiten in der berechneten Geschwindigkeit führen; vor allem relativ zu kurzen Zykluszeiten. In EtherCAT werden Positionsmessungen durch die präzise, lokale Clock getriggert und nicht durch das Bussystem. Dies führt zu einer deutlich höheren Genauigkeit.

Zusätzlich wird das MainDevice durch den Einsatz von DCs entlastet. Positionsmessungen werden durch die lokale Clock getriggert und nicht durch den Empfang eines Frames. Deshalb unterliegt das MainDevice keinen strengen Anforderungen bzgl. dem Senden der Frames. Dadurch kann das MainDevice in Software auf Standard Ethernet-Hardware implementiert werden. Ein Jitter im Bereich von einigen Mikrosekunden verhindert nicht Genauigkeit der DCs. Die Genauigkeit der Clock ist unabhängig vom Zeitpunkt, an dem sie gesetzt wird. Deshalb ist die absolute Transmissionszeit des Frames irrelevant. Das EtherCAT MainDevice muss lediglich sicherstellen, dass der EtherCAT Frame gesendet wird, bevor das DC-Signal den Output der SubDevices triggert [Eth].

### 2.3.6. Diagnose und Fehlerlokalisierung

Erfahrungen mit konventionellen Feldbussen haben gezeigt, dass Diagnosecharakteristiken eine bedeutende Rolle spielen, wenn die Verfügbarkeit eines Geräts und dessen Inbetriebnahmedauer bestimmt werden soll. Zusätzlich zur Fehlererkennung ist Fehlerlokalisierung wichtig beim Troubleshooting. EtherCAT verfügt über das Feature, die aktuelle Netzwerktopologie während des Hochfahrens des Netzes zu scannen und mit der geplanten Topologie zu vergleichen. EtherCAT hat weitere Diagnosefähigkeiten inhärent zu seinem System.

Der ESC jedes SubDevices prüft den Frame auf Fehler anhand der Checksumme. Die Informationen werden der Applikation bereitgestellt, sofern der Frame ohne Fehler empfangen wurde. Sollte ein Fehler vorliegen, wird der **Error Counter** inkrementiert und alle folgenden Nodes darüber informiert. Das MainDevice wird ebenfalls feststellen, dass der Frame fehlerbehaftet ist und die Daten verwerfen. Das MainDevice kann anhand der Error Counter der SubDevices feststellen, wo der Fehler aufgetreten ist. Dies stellt einen enormen Vorteil im Gegensatz zu konventionellen Feldbussen dar, da dort der Fehler über den gesamten Bus weitergegeben wird, was es unmöglich macht den Ursprung des Fehlers zu lokalisieren. EtherCAT kann gelegentlich auftretende Unterbrechungen detektieren und lokalisieren, bevor der Vorfall andere Geräte beeinflussen kann.

Bei gleicher Zykluszeit ist die Wahrscheinlichkeit von Störungen durch Bitfehler innerhalb eines EtherCAT Frames wesentlich geringer. Dadurch ist EtherCATs einzigartiges Prinzip der Bandbreitennutzung um Größenordnungen besser als bei Ethernet Technologien, welche Single-Frames nutzen. Werden deutlich kürzere Zykluszeiten verwendet, wird die Zeit der

Fehlerbehebung drastisch reduziert. Dadurch wird es auch einfacher solche Probleme in der Applikation zu adressieren.

Die Informationen innerhalb eines Frames können anhand des **Working Counters** besser auf Konsistenz gemonitort werden. Jedes verfügbare Node inkrementiert den Working Counter automatisch, sofern es durch das Datagramm adressiert und sein Speicher ausgelesen werden kann. Das MainDevice kann dann zyklisch bestätigen, dass alle Nodes mit konsistenten Daten arbeiten. Wenn der Working Counter einen abweichenden Wert beinhaltet, leitet das MainDevice das Datagramm nicht an die Kontrollapplikation weiter. Mit Hilfe von Status- und Fehlermeldungen der Nodes und des Link-Status, ist es dem MainDevice automatisch möglich den Grund für das unerwartete Verhalten festzustellen. Aufgrund der Tatsache, dass EtherCAT in Standard Ethernet Frames eingebettet ist, ist es möglich den Netzwerkverkehr mit Hilfe von freien Ethernet Tools aufzunehmen. Beispielsweise hat Wireshark<sup>7</sup> einen EtherCAT Protokoll Dissektor bereits integriert. So können protokollspezifische Informationen wie der Working Counter, Kommandos und weitere direkt als Klartext ausgegeben werden. Weitere nützliche Informationen können unter den folgenden beiden Links eingesehen werden [Eth]:

[EtherCAT Diagnosis for Users](#)

[EtherCAT Diagnosis for Developers](#)

### 2.3.7. Anforderung an hohe Verfügbarkeit

Kabelbrüche oder fehlfunktionierende Nodes sollten in Geräten mit hohen Anforderungen an die Verfügbarkeit nicht dazu führen, dass das gesamte Netzwerksegment nicht mehr verfügbar ist. EtherCAT stellt die Redundanz von Kabeln mit einfachen Maßnahmen zur Verfügung. Durch eine Kabelverbindung zwischen dem letzten Node und einem zusätzlichen Port am MainDevice, wird die Bustopologie zu einer Ringtopologie erweitert. Fälle, in denen redundant umgeschalten werden muss (z.B. Kabelbrüche oder fehlfunktionierende Nodes), werden durch ein Software Add-On im Stack des MainDevice erkannt. Die Nodes selbst müssen dafür nicht angepasst werden und wissen nicht darüber Bescheid, dass sie aktuell in einem redundantem Netz betrieben werden. Link Detection in den SubDevices erkennt und löst redundante Fälle automatisch mit einer Recovery-Time  $\leq 15\mu\text{s}$ . So wird maximal ein einziger Kommunikationszyklus unterbrochen. Das bedeutet, dass sogar Motion Applications mit kurzen Zykluszeiten weiterarbeiten können, wenn ein Kabel bricht. Mit EtherCAT ist es auch möglich das MainDevice redundant in einem Hot-Standby Modus zu betreiben. Anfällige Netzwerkkomponenten, wie z. B. solche, die mit einer Drag Chain verbunden sind, können mit einer Stichleitung verkabelt werden, so dass selbst bei einem Kabelbruch der Rest der Maschine weiterläuft [Eth].

---

<sup>7</sup>[Wireshark Website](#)

Abbildung 2.10.: Billige Kabelredundanz bei Standard EtherCAT SubDevices

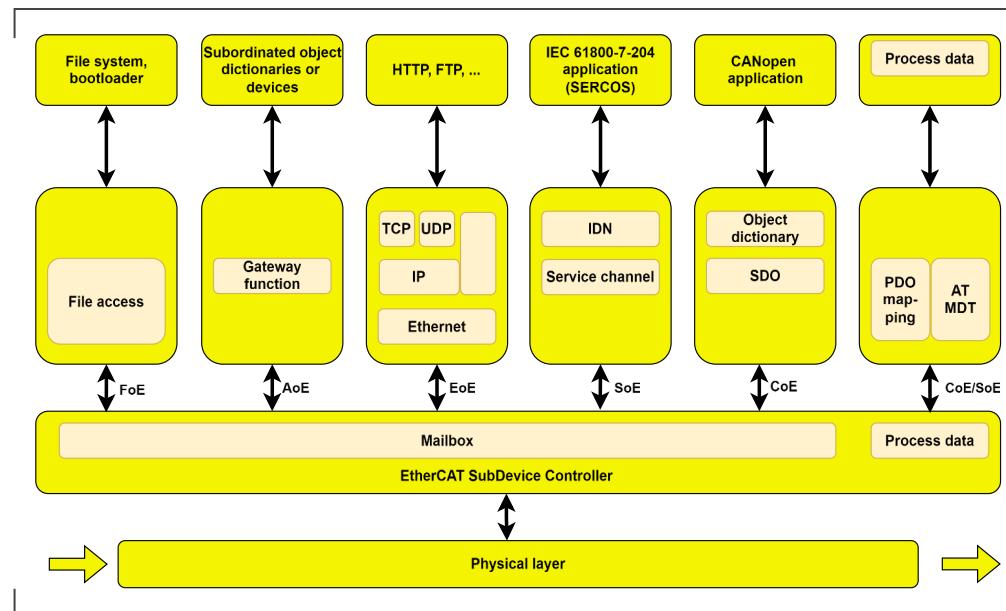

### 2.3.8. Mailbox und Kommunikationsprofile

Um SubDevices konfigurieren und Diagnosen anfertigen zu können, ist es mit Hilfe von azyklischer Kommunikation möglich auf Variablen, welche das Netzwerk betreffen, zuzugreifen. Sie basieren auf dem zuverlässigen Mailbox-Protokoll, welches über eine Auto-Recover Funktion für fehlerbehaftete Nachrichten verfügt. Um eine breite Auswahl an Geräten und Anwendungslayern unterstützen zu können, wurden die folgenden EtherCAT Kommunikationsprofile eingeführt:

- ↗ CAN<sup>8</sup> application protocol over EtherCAT (CoE)

- ↗ Servo drive profile, according to IEC 61800-7-204<sup>9</sup> (SoE)

- ↗ Ethernet over EtherCAT (EoE)

- ↗ File Access over EtherCAT (FoE)

- ↗ Automation Device Protocol over EtherCAT (ADS over EtherCAT, AoE)

Ein SubDevice muss nicht alle Kommunikationsprofile unterstützen. Es entscheidet selbst, welches Profil für die Anforderungen am besten geeignet ist. Das MainDevice wird anhand des SubDevice Description Files in Kenntnis gesetzt, welche Profile implementiert sind [Eth]. Diese Profile wurden eingeführt, um eine breitere Masse an Feldgeräten und infolgedessen auch Application Layers ansprechen zu können. Im Gegensatz zu zyklischen Prozessdaten gibt es für azyklische Kommunikation keine Garantie, dass die Daten in Echtzeit ausgeliefert

<sup>8</sup>Controller Area Network

<sup>9</sup>IEC 61800-7-204

Abbildung 2.11.: **Koexistenz von verschiedenen Kommunikationsprofilen im selben System**

werden [gmb].

### 2.3.9. Fieldbus Memory Management Unit

Die Fieldbus Memory Management Unit (FMMU) befindet sich im Data Link Layer und ist in jedem SubDevice integriert. FMMUs werden für die logischen EtherCAT Kommandos benutzt, welche üblicherweise mit nur einem Frames ausgetauscht werden und so die zyklische Kommunikation realisieren. FMMUs implementieren logische Adressen bit- oder byteweise auf die physikalischen Adressen des ESCs.

Während des Bootvorgangs konfiguriert das MainDevice die FMMU aller SubDevices. Dadurch wird dem Bereich des logischen Prozessdatenabildes ein lokaler Adressraum zugeordnet. Jeder FMMU-Kanal ordnet einen kontinuierlichen logischen Adressraum einem kontinuierlichen physikalischen Adressraum auf dem SubDevice zu. Die FMMU entnimmt dem durchlaufendem Telegramm Daten und fügt welche hinzu. Das Delay beträgt hierbei nur wenige Nanosekunden [Teca].

### 2.3.10. SyncManager

Der SyncManager ist für Datenkonsistenz und sicheren Datenaustausch zwischen MainDevice und den Applikationen auf den SubDevices verantwortlich. Er schützt einen DPRAM<sup>10</sup>-Bereich vor gleichzeitigem Zugriff. Das MainDevice konfiguriert die SyncManager auf den SubDevices. Dabei werden die Richtung und die Art und Weise der Kommunikation festgelegt. Dafür steht ein Datenpuffer zur Verfügung. Es gibt zwei Arten von Sync-Managern:

- ↗ Buffered-Type-SyncManager (Drei-Buffer-SyncManager)

- genutzt für zyklische Prozessdatenkommunikation

- drei physikalisch Buffer mit identischer Größe

- immer ein freier Buffer zum Schreiben

- immer ein konsistenter Buffer zum Lesen (außer beim ersten Mal Schreiben)

- Lesen und Schreiben ist zu jeder Zeit für Main- und SubDevices möglich

- wird schneller geschrieben als gelesen, gehen ältere Daten verloren

- die Adressen des Buffers werden in der SyncManager Konfiguration eingestellt

- Zugriffe auf den ersten Bereich des Buffers, werden an die drei Buffer weitergeleitet

- andere SyncManager werden so konfiguriert, dass sie den Speicherbereich des zweiten und dritten Buffers nicht adressieren

- ein Buffer wird für Schreibzugriff dem Producer zugeordnet; ein anderer Buffer dem Consumer für Lesezugriff; ein Buffer hält die Daten konsistent

- ↗ Mailbox-Type-SyncManager (Ein-Buffer-SyncManager)

- genutzt für Mailboxkommunikation der Protokolle der SubDevice-Applikationsschicht

- ein Buffer mit zuvor konfigurierter Größe

<sup>10</sup>Dual-Port RAM

- Schutz vor Datenüberlauf

- Leseseite liest, bevor Schreibseite schreiben kann und vice-versa → Buffer wird nach Zugriff gesperrt

- Handshake zwischen Main- und SubDevice für Datenaustausch [Teca]

### 2.3.11. Implementierung von EtherCAT Interfaces

Die EtherCAT-Technologie wurde speziell für ein kostengünstiges Design optimiert, so dass das Hinzufügen einer EtherCAT-Schnittstelle zu einem Sensor, I/O-Gerät oder Embedded-Controller die Gerätekosten nicht wesentlich erhöhen sollte. Darüber hinaus erfordert die EtherCAT-Schnittstelle auch keine leistungsstärkere CPU - die CPU-Anforderungen richten sich lediglich nach den Anforderungen der Zielanwendung. Bei der Entwicklung einer Schnittstelle sind neben den Hard- und Softwareanforderungen auch der Entwicklungssupport und die Verfügbarkeit von Kommunikationsstacks wichtig. Die EtherCAT Technology Group bietet weltweiten Entwicklersupport, um Fragen oder technische Probleme schnell zu beantworten. Evaluierungskits verschiedener Hersteller, Entwickler-Workshops sowie kostenloser Beispielcode erleichtern den Einstieg in die Entwicklung. Für den Endanwender ist der wichtigste Faktor die Interoperabilität von EtherCAT-Geräten verschiedener Hersteller. Um die Interoperabilität zu gewährleisten, sind die Gerätehersteller verpflichtet, einen Konformitätstest durchzuführen, bevor sie ihr Gerät auf den Markt bringen. Der Test prüft, ob die Implementierung der EtherCAT-Spezifikation entspricht, und kann mit dem EtherCAT Conformance Test Tool durchgeführt werden. Der Test kann auch während der Geräteentwicklung eingesetzt werden, um Implementierungsprobleme frühzeitig zu erkennen und zu korrigieren [Eth].

#### MainDevice

Die Schnittstelle für ein EtherCAT MainDevice hat eine einzige, unglaublich einfache Hardwareanforderung: einen Ethernet-Port.

Die Implementierung verwendet entweder den On-Board-Ethernet-Controller oder eine kostengünstige Standard-Netzwerkkarte, so dass keine spezielle Schnittstellenkarte erforderlich ist. Das bedeutet, dass ein MainDevice mit nur einem Standard-Ethernet-Port eine harte Echtzeit-Netzwerklösung implementieren kann.

In den meisten Fällen ist der Ethernet-Controller über Direct Memory Access (DMA) integriert, so dass keine CPU-Kapazität für die Datenübertragung zwischen dem MainDevice

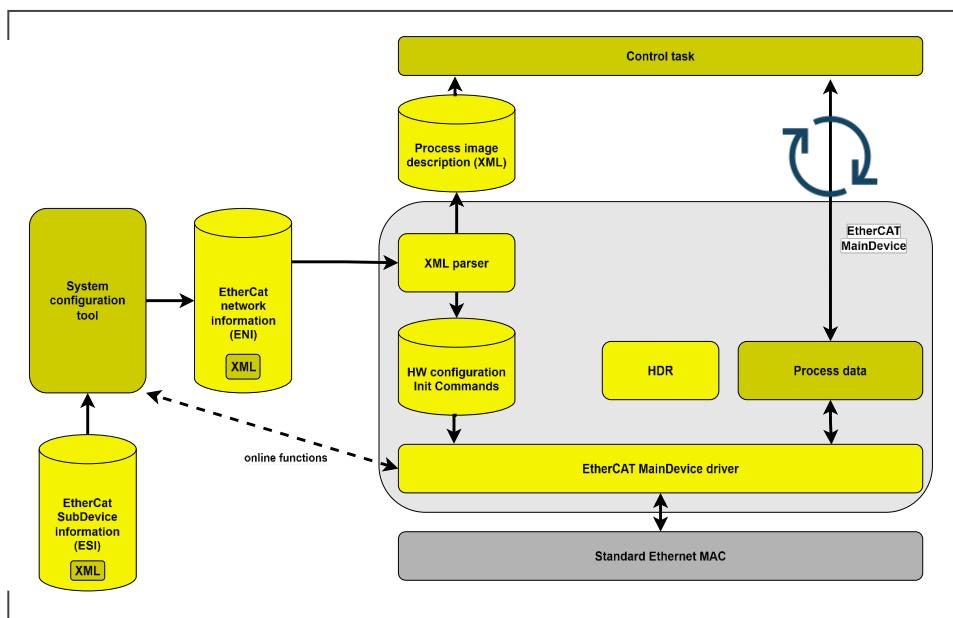

und dem Netzwerk benötigt wird. In einem EtherCAT-Netzwerk erfolgt das Mapping bei den SubDevices. Jedes SubDevice schreibt seine Daten an die richtige Stelle im Prozessabbild und liest die an es adressierten Daten, während der Frame des Device durchläuft. Daher ist das Prozessabbild, das am MainDevice ankommt, bereits korrekt sortiert. Da die MainDevice-CPU nicht mehr für die Sortierung zuständig ist, hängen ihre Leistungsanforderungen nur noch von der gewünschten Anwendung und nicht von der EtherCAT-Schnittstelle ab. Besonders für kleine, mittlere und klar definierte Anwendungen ist die Implementierung eines EtherCAT MainDevices sehr einfach. EtherCAT MainDevices sind für eine Vielzahl von Betriebssystemen implementiert worden wie bspw. Windows und Linux in verschiedenen Iterationen, QNX, RTX, VxWorks, Intime, eCos. Die ETG-Mitglieder bieten eine Vielzahl von

Abbildung 2.12.: Typische EtherCAT MainDevice Architektur

Optionen an, um die Implementierung eines EtherCAT MainDevice zu unterstützen. Diese reichen vom kostenlosen Download der EtherCAT MainDevice Libraries über Beispielcode für MainDevices bis hin zu Kompletpaketen (inklusive Services) für verschiedene Echtzeit-Betriebssysteme und CPUs.

Um ein Netzwerk zu betreiben, benötigt das EtherCAT MainDevice die zyklische Prozessdatenstruktur sowie Boot-Up-Kommandos für jedes SubDevice. Diese Kommandos können mit Hilfe eines EtherCAT-Konfigurationstools, das die EtherCAT SubDevice Information (ESI)-Dateien der angeschlossenen Geräte verwendet, in eine EtherCAT-Network-Information-(ENI)-Datei exportiert werden.

Der Umfang der verfügbaren MainDevice-Implementierungen und ihrer unterstützten Funktionen variiert. Je nach Zielanwendung werden optionale Funktionen unterstützt oder

bewusst weggelassen, um die Auslastung der Hard- und Softwareressourcen zu optimieren. Aus diesem Grund werden EtherCAT MainDevices in zwei Klassen eingeteilt:

- ein Class-A-MainDevice ist ein Standard EtherCAT MainDevice

- ein Class-B-MainDevice ist ein MainDevice mit weniger Funktionen

Grundsätzlich sollten alle MainDevice-Implementierungen eine Class-A-Klassifizierung anstreben. Die Klasse B wird nur für Fälle empfohlen, in denen die verfügbaren Ressourcen nicht ausreichen, um alle Funktionalitäten zu unterstützen, wie z. B. in eingebetteten Systemen [Eth].

### SubDevice

EtherCAT SubDevices nutzen kostengünstige EtherCAT-SubDevice-Controller (ESC) in Form eines ASICs, FPGAs oder integriert in einen Standard-Mikrocontroller. Einfache SubDevices benötigen nicht einmal einen zusätzlichen Mikrocontroller, da die Ein- und Ausgänge direkt an den ESC angeschlossen werden können. Bei komplexeren SubDevices hängt die Kommunikationsleistung nur geringfügig von der Leistung des Mikrocontrollers ab.

Die Hardwarekonfiguration wird in einem non-volatile Speicher (z. B. einem EEPROM) -

Abbildung 2.13.: SubDevice Hardware: ESC mit direktem I/O

dem SubDevice Information Interface (SII) - gespeichert, der Informationen über die grundlegenden Geräteeigenschaften enthält. Dadurch kann das MainDevice diese beim Hochfahren lesen und das Gerät betreiben, auch wenn die Gerätebeschreibungsdatei nicht verfügbar ist. Die mit dem Gerät gelieferte ESI-Datei ist XML-basiert und enthält die vollständige Beschreibung seiner über das Netzwerk zugänglichen Eigenschaften. Dazu zählen Informationen wie z. B. Prozessdaten und deren Mapping-Optionen, die unterstützten Mailbox-Protokolle einschließlich optionaler Funktionen sowie die unterstützten Synchronisationsmodi.

Auf der ETG-Website findet sich ein SubDevice Implementation Guide mit nützlichen Tipps und Hinweisen auf weiterführende Dokumentationen zur Implementierung von SubDevices [Eth]:

[EtherCAT SubDevice Implementation Guide](#)

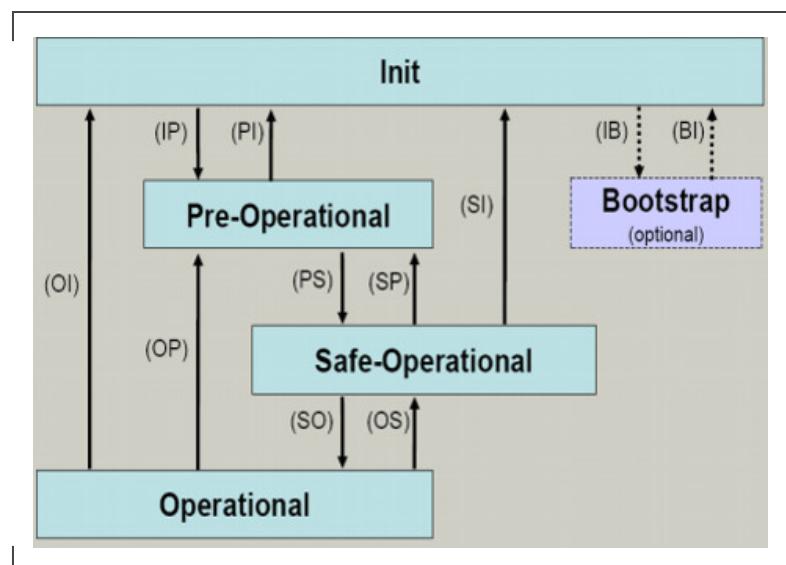

### 2.3.12. EtherCAT State Machine

EtherCAT SubDevices werden durch das MainDevice gesteuert. Dafür gibt es in den SubDevices die EtherCAT State Machine (ESM). Je nach State sind verschiedene Funktionen auf den SubDevices ausführbar. Vor allem während des Initialisierungs-Prozesses müssen spezifische Befehle vom MainDevice an die SubDevices gesendet werden. Es gibt folgende States:

- ↗ Initialisierung (INIT)

- ↗ Pre-Operational (PREOP)

- ↗ Safe-Operational (SAFEOP)

- ↗ Operational (OP)

- ↗ Wartungszustand (BOOT)

Die einzelnen States werden in den folgenden Unterkapiteln erklärt. Die möglichen Übergänge zwischen den States sind in Abbildung 2.14 zu sehen. Nach dem Bootvorgang des SubDevices befindet es sich regulär im State OP [Tecc].

Abbildung 2.14.: EtherCAT State Machine [Tecc]

### INIT State

- ↗ Zustand nach Einschalten des Geräts

- ↗ weder Mailbox- noch Prozessdatenkommunikation möglich

- ↗ für die Mailbox-Kommunikation initialisiert das MainDevice die Sync-Manager-Kanäle 0 und 1 [Tecc]

Im INIT-State führt das MainDevice eine Discovery des Busses und somit der angeschlossenen SubDevices durch. Dafür wird die Auto Increment Address genutzt.

### PREOP State

- ↗ beim Übergang INIT → PREOP überprüft das SubDevice, ob die Mailbox korrekt initialisiert wurde

- ↗ Mailbox-Kommunikation möglich (sofern Mailbox-Support vorhanden) ; Prozessdatenkommunikation nicht

- ↗ das MainDevice initialisiert:

- Sync-Manager-Kanäle (ab Kanal 2) für die Prozessdaten

- FMMU Kanäle

- PDO-Mapping oder Sync-Manager-PDO-Assignment, sofern auf SubDevice verfügbar

- ↗ Übertragung der Einstellungen für Prozessdatenübertragung sowie ggf. klemmenspezifische Parameter, welche von den Defaulteinstellungen abweichen [Tecc]

### SAFEOP State

- ↗ beim Übergang PREOP → SAFEOP überprüft das SubDevice, ob die Sync-Manager-Kanäle für Prozessdatenkommunikation und die Einstellungen der DCs korrekt initialisiert wurde

- ↗ Mailbox-Kommunikation und Prozessdatenkommunikation möglich

- ↗ das SubDevice kopiert Input-Daten in den entsprechenden DPRAM-Bereich des ESCs

- ↗ das SubDevice hält seine Outputs im sicheren Zustand und gibt diese nicht aus

- ↗ Input-Daten werden am SubDevice zyklisch aktualisiert [Tecc]

### OP State

- ↗ vor dem Übergang SAFEOP → OP müssen bereits gültige Output-Daten übertragen werden

- ↗ Mailbox-Kommunikation und Prozessdatenkommunikation möglich

- ↗ das SubDevice kopiert seine Ausgangsdaten auf seine Ausgänge [Tecc]

### BOOT State

- genutzt für: Wartung und Firmwareupdate der SubDevices

- Mailbox-Kommunikation nur via FoE möglich

- Prozessdatenkommunikation nicht möglich [Tecc]

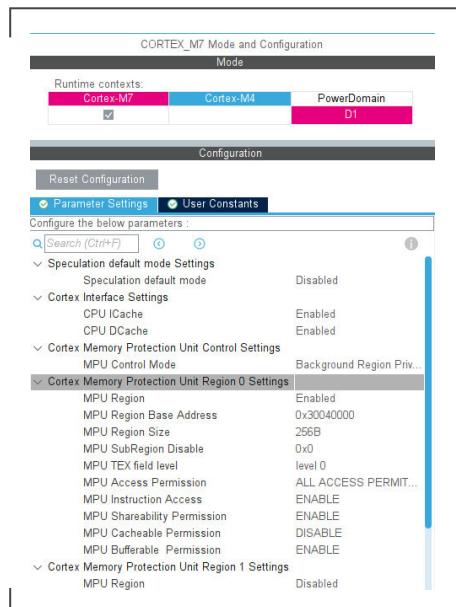

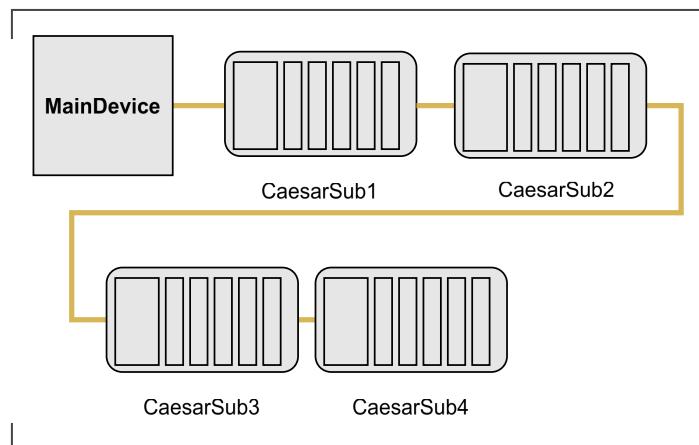

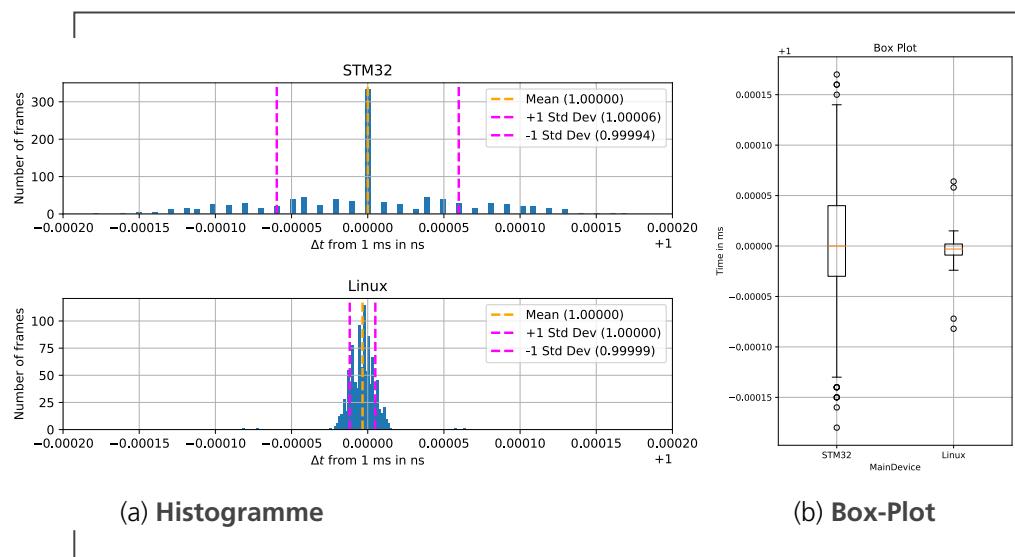

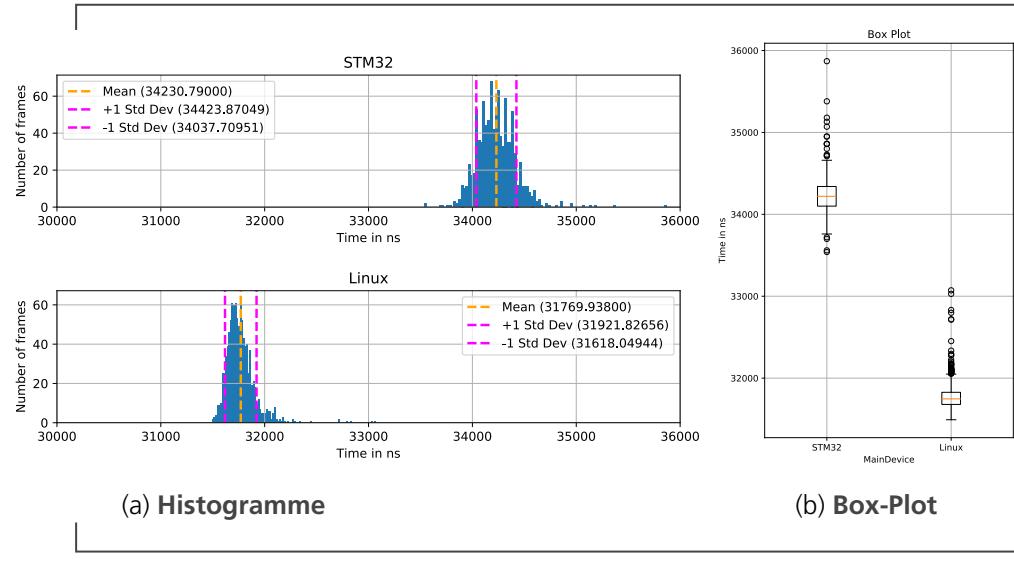

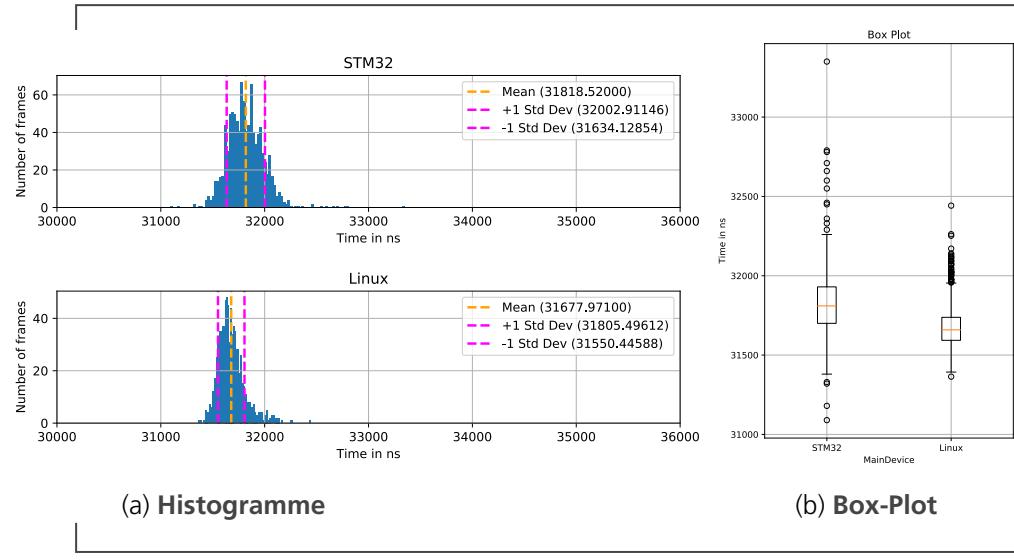

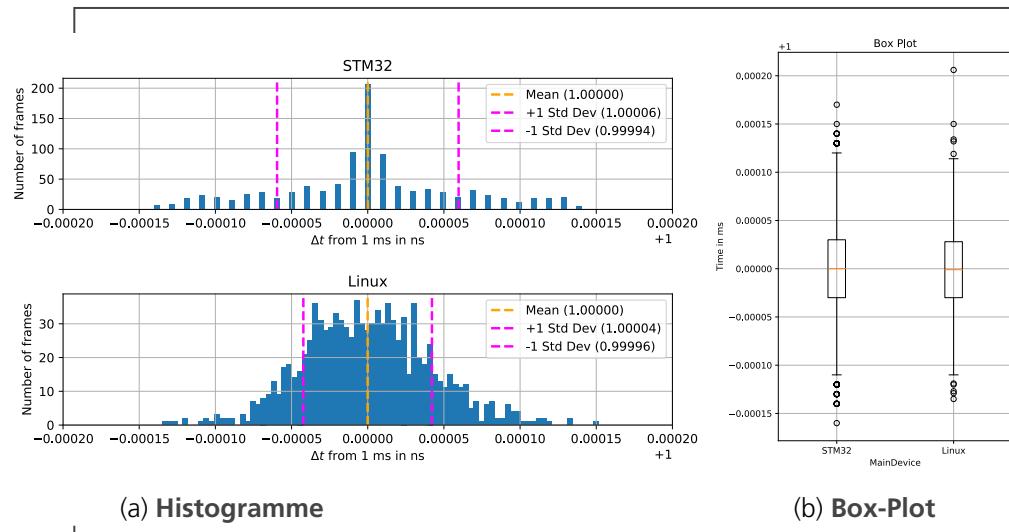

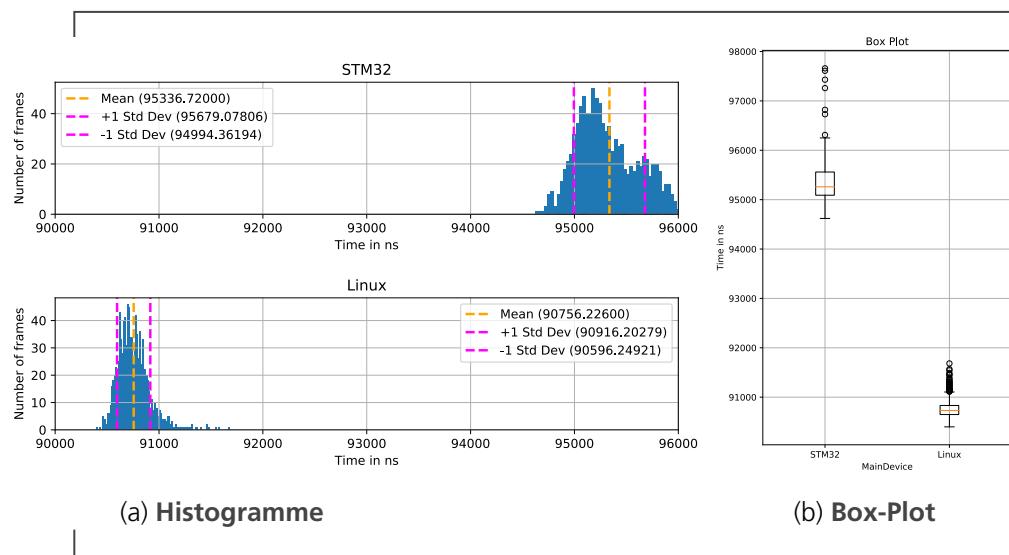

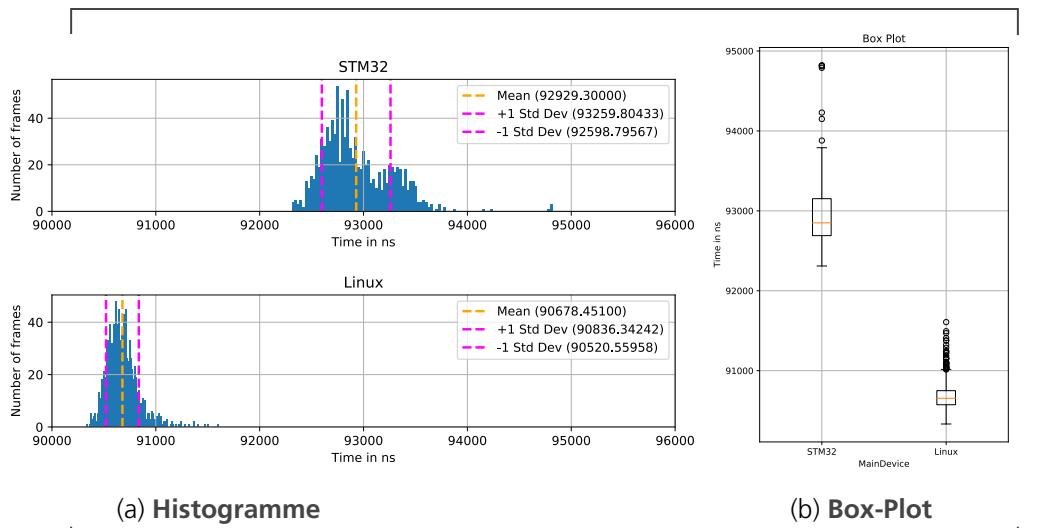

### 2.3.13. Working Counter