# APPLICATION-AWARE BENCHMARKING OF NISQ HARDWARE

Joe Harris & Peter Schuhmacher, 21 March 2025

#### **Abstract**

- Inputs:

- Quantum circuit U (application) consisting of single and two-qubit Pauli rotations

- Pauli observable *0* to measure on that circuit

- Target hardware

- Optional: QEM method, etc.

- Aim: benchmark the fidelity  $F = \langle O \rangle_{U,\text{noisy}} / \langle O \rangle_{U,\text{ideal}}$  on target hardware

- Issue: we don't know ideal value  $\langle O \rangle_{U,ideal}$

- Output:

- Family of Clifford benchmarking circuits  $V_i$  such that

$$\frac{\langle O \rangle_{V_i, \text{noisy}}}{\langle O \rangle_{V_i, \text{ideal}}} \approx F$$

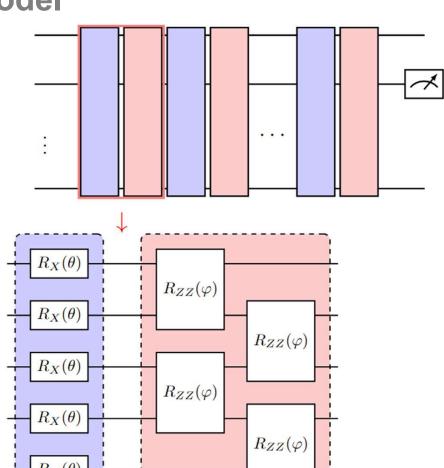

## Example application: quantum simulation of kicked-Ising model

$$H = -J \sum_{\langle i,j \rangle} Z_i Z_j + h \sum_i X_i$$

$$\downarrow$$

$$\psi$$

$$e^{-iHt} = [\underline{L_2L_1}]^n + \mathcal{O}\left(\frac{t^2}{n}\right)$$

- Circuit consists of repeated Trotter layers

- Layers consist of single and two-qubit Pauli rotation gates

- *Z* measurement on single qubit

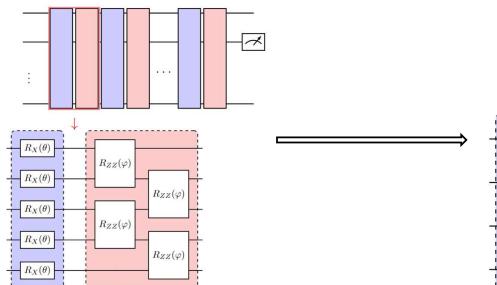

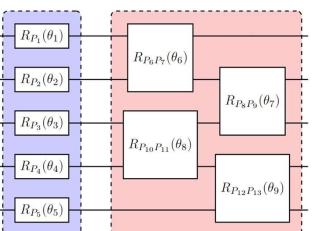

where  $P_i \in \{X, Y, Z\}$  and  $\theta_i \in \{k\pi/2, k = 0,1,2,3\}$ .

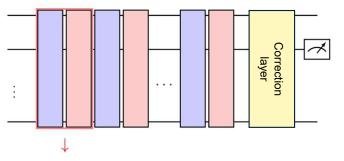

- Pick Paulis *P<sub>i</sub>* such that output state is a known product state of Pauli eigenstates

- Apply 'correction layer' of single qubit gates to move state to +1-eigenstate of O, then  $\langle O \rangle_{V_i, \text{ideal}} = 1$  and  $\langle O \rangle_{V_i, \text{noisy}} \approx F$

- Requirement: benchmarking circuit and application circuit have same error behaviour when running on hardware

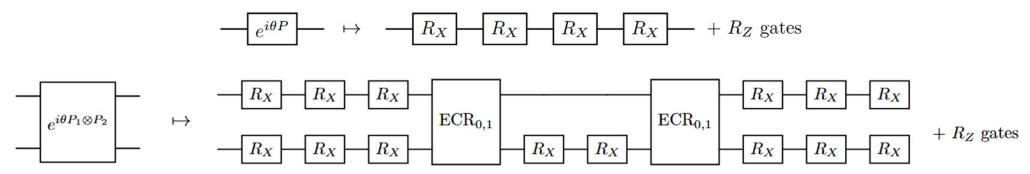

#### Rigid compilation rules for specific hardware

- We impose rigid compilation rules on Pauli rotations to keep circuit structure consistent

- E.g. IBM hardware has basis gates set  $\{\sqrt{X}, X, R_Z(\theta), ECR\}$ , where  $R_Z(\theta)$  is error-free [1]

where each  $R_X \in \{\sqrt{X}, X\}$

- Possible assumptions:

- Similar error for all single-qubit gates

- Two-qubit gate error >> single-qubit gate error

#### [Cliffordise, compile] or [compile, Cliffordise]?

- A DUR

- Can benchmark generic circuits (not just Pauli rotations) by first compiling to hardware, then Cliffordising

- E.g. IBM hardware has basis gate set  $\{ECR, X, \sqrt{X}, R_Z(\theta)\}$ , so can Cliffordise by setting each  $R_Z$  rotation angle to nearest multiple of  $\frac{\pi}{2}$

- Also useful but less control over  $\langle O \rangle_{ideal}$

- IBM recently announced *Noisy Estimation Analyser Tool (NEAT)* which does this (qiskit\_ibm\_runtime.debug\_tools.Neat)

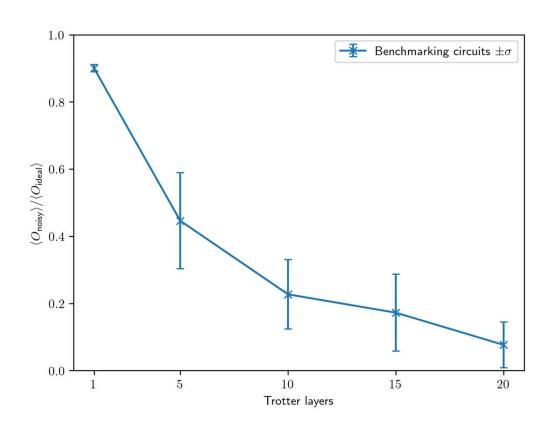

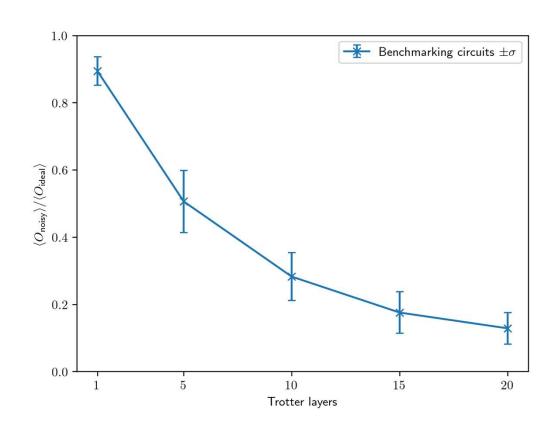

- Results from ibm\_brisbane with 16 qubits

- 10 benchmarking circuits per datapoint

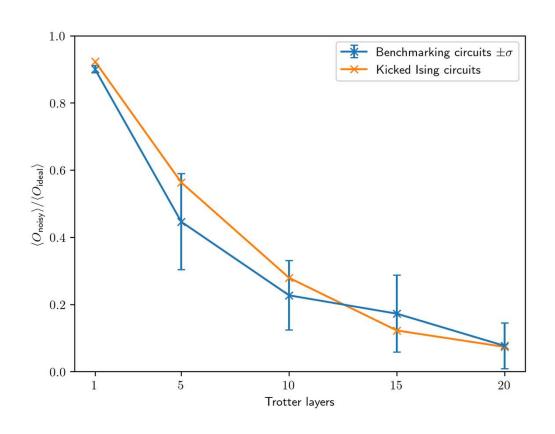

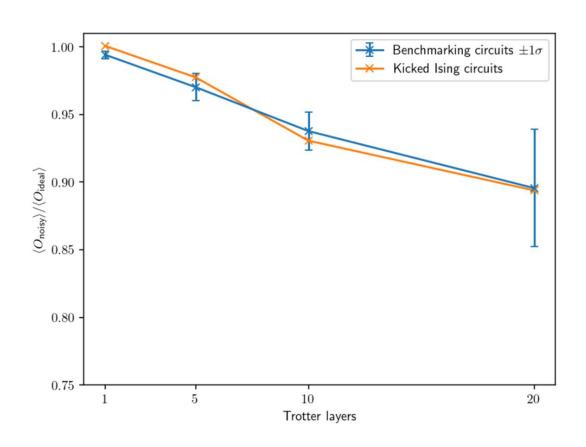

- Results from ibm\_brisbane with 16 qubits

- 10 benchmarking circuits per datapoint

- 1 application circuit per datapoint

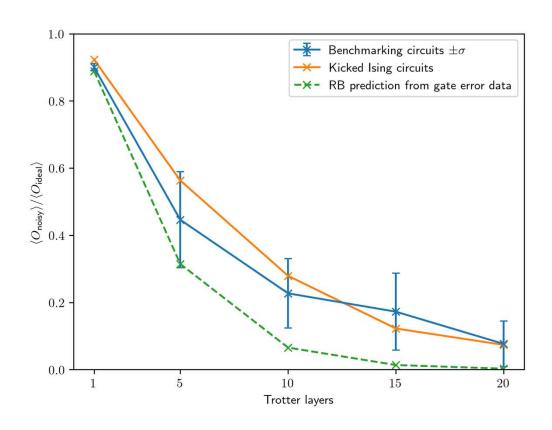

- Results from ibm\_brisbane with 16 qubits

- 10 benchmarking circuits per datapoint

- 1 application circuit per datapoint

- RB prediction from live gate error rates

- Results from ibm\_brisbane with 127 qubits

- 10 benchmarking circuits per datapoint

#### **Benchmarking QEM methods**

- 10-qubit noisy simulation using ZNE + Pauli twirling

- Gate-wise depolarising noise

- 10 benchmarking circuits, 1 kicked Ising circuit per datapoint

- 3 amplified noise levels (1,3,5) per circuit

- 25 Pauli twirling repetitions per noise level

### Thanks!

joseph.harris@dlr.de peter.schuhmacher@dlr.de