# THÈSE DE DOCTORAT DE

### NANTES UNIVERSITÉ

ÉCOLE DOCTORALE Nº 641

Mathématiques et Sciences et Technologies de l'Information et de la Communication

Spécialité: Électronique

Par

# **Quentin DARIOL**

# Early Timing and Energy Prediction and Optimization of Artificial Neural Networks on Multi-Core Platforms

Thèse présentée et soutenue à Nantes, France, le 27/11/2023 Unité de recherche : IETR UMR CNRS 6164

#### Rapporteurs avant soutenance:

Prof. Dr. Matthias JUNG Full professor, Würzburg Universität, Germany

Dr. Angeliki KRITIKAKOU Associate professor - HDR, IRISA/INRIA, Université de Rennes, France

#### **Composition du Jury:**

Président : Prof. Dr. Frédéric PÉTROT Full professor, TIMA, Université Grenoble Alpes, France

Examinateurs: Dr. Kim GRÜTTNER Head of department, German Aerospace Center (DLR), Germany

Prof. Dr. Matthias JUNG Full professor, Würzburg Universität, Germany

Dr. Angeliki KRITIKAKOU Associate professor - HDR, IRISA/INRIA, Univ. Rennes, France

Prof. Dr. Gregor SCHIELE Full professor, Duisburg-Essen Universität, Germany

Dir. de thèse : Prof. Dr. Sébastien PILLEMENT Full professor, IETR, Nantes Université, France

Encadrant : Dr. Sébastien LE NOURS Associate professor - HDR, IETR, Nantes Université, France

#### Invité:

Dr. Domenik HELMS Principal scientist, German Aerospace Center (DLR), Germany

# Table of Contents

| Ré  | sumé  | long     |                                                        | 17 |

|-----|-------|----------|--------------------------------------------------------|----|

| Acl | know  | ledgeme  | ent                                                    | 25 |

| Ι   | Int   | roductio | on                                                     | 27 |

|     | I.1   | Conte    | xt                                                     | 27 |

|     |       | I.1.1    | Artificial Intelligence (AI) and Neural Networks (NNs) | 27 |

|     |       | I.1.2    | Internet of Things (IoT) and TinyML                    | 29 |

|     |       | I.1.3    | Available platforms at the edge                        | 30 |

|     |       | I.1.4    | NN deployment on embedded platforms                    | 33 |

|     | I.2   | Resear   | ch challenges                                          | 35 |

|     | I.3   | Contri   | butions                                                | 35 |

|     | I.4   | Organ    | ization                                                | 36 |

| II  | Rel   | lated wo | ork                                                    | 39 |

|     | II.1  | Evalua   | ation of NN deployments on edge platforms              | 39 |

|     |       | II.1.1   | Rapid prototyping                                      | 40 |

|     |       | II.1.2   | Evaluation using models                                | 43 |

|     | II.2  | Design   | Space Exploration (DSE)                                | 50 |

| III | Wo    | rk hypo  | othesis                                                | 53 |

|     | III.1 | Consid   | lered types of NNs                                     | 53 |

|     | III.2 | Descri   | ption of NNs in Synchronous Data Flow (SDF)            | 57 |

|     |       | III.2.1  | SDF Model of Computation (MoC)                         | 57 |

|     |       | III.2.2  | Modeling of NNs in SDF                                 | 59 |

|     | III.3 | Model    | of Architecture (MoA)                                  | 62 |

|     |       | III.3.1  | Composition of the MoA                                 | 62 |

|     |       | III.3.2  | Power management within the MoA                        | 65 |

## TABLE OF CONTENTS

|              | III.4 | Mappi    | ing of NNs modeled in SDF on platforms respecting the MoA                                                                                                                                                  | 67         |

|--------------|-------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|              | III.5 | Real p   | olatform prototype implementation and considered applications                                                                                                                                              | 69         |

| IV           | Sin   | nulation | a-based timing properties prediction approach                                                                                                                                                              | <b>7</b> 5 |

|              | IV.1  | Timin    | g modeling and prediction flow overview                                                                                                                                                                    | 75         |

|              | IV.2  | Comp     | utation time modeling approach                                                                                                                                                                             | 78         |

|              |       | IV.2.1   | Analytical computation time models                                                                                                                                                                         | 78         |

|              |       | IV.2.2   | Measurement-based characterization approach for computation                                                                                                                                                |            |

|              |       |          | time models $\dots$                                                                                                                                                                                        | 82         |

|              | IV.3  | Comm     | nunication time modeling approach                                                                                                                                                                          | 84         |

|              |       | IV.3.1   | Analytical timing model for token production/reading in shared                                                                                                                                             |            |

|              |       |          | memory                                                                                                                                                                                                     | 84         |

|              |       | IV.3.2   | Message level communication time model                                                                                                                                                                     | 85         |

|              |       | IV.3.3   | Measurement-based characterization approach for the communi-                                                                                                                                               |            |

|              |       |          | cation time model                                                                                                                                                                                          | 86         |

|              | IV.4  | Simula   | ation model description in SystemC                                                                                                                                                                         | 87         |

|              | IV.5  | Exper    | iment results                                                                                                                                                                                              | 89         |

|              |       | IV.5.1   | Tested scenarios                                                                                                                                                                                           | 89         |

|              |       | IV.5.2   | Pure analytical model for comparison against the simulation $\ .$ .                                                                                                                                        | 90         |

|              |       | IV.5.3   | Validation results                                                                                                                                                                                         | 90         |

|              | IV.6  | Discus   | ssions                                                                                                                                                                                                     | 93         |

|              | IV.7  | Conclu   | usion                                                                                                                                                                                                      | 96         |

| $\mathbf{V}$ | Pov   | wer and  | energy modeling and analysis flow                                                                                                                                                                          | 99         |

|              | V.1   | Power    | modeling and analysis flow overview $\ \ldots \ \ldots \ \ldots \ \ldots$                                                                                                                                  | 99         |

|              | V.2   | Power    | $\  \   model\ proposal\ \ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots$                                                                                                                           | 101        |

|              | V.3   | Power    | $model\ calibration\ \dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots$ | 107        |

|              |       | V.3.1    | Calibration methodology                                                                                                                                                                                    | 107        |

|              |       | V.3.2    | Application of the calibration and results                                                                                                                                                                 | 114        |

|              | V.4   | Integra  | ation in the simulation flow and energy prediction                                                                                                                                                         | 118        |

|              | V.5   | Evalua   | ation of the power modeling flow                                                                                                                                                                           | 119        |

|              |       | V.5.1    | Analytical power and energy model for comparison                                                                                                                                                           | 119        |

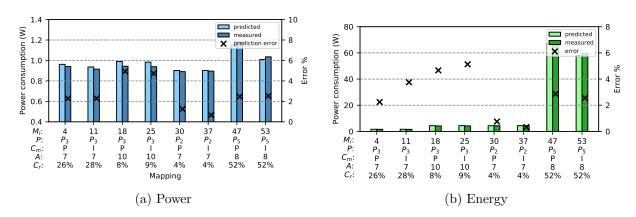

|              |       | V.5.2    | Evaluation on a fixed multi-core platform                                                                                                                                                                  | 120        |

|              |       | V.5.3    | Evaluation of the scalability in regards to the number of tiles                                                                                                                                            |            |

|              |       |          | and private memory size                                                                                                                                                                                    | 127        |

|                        | V.6     | Concl    | usion                                                                  | 132 |

|------------------------|---------|----------|------------------------------------------------------------------------|-----|

|                        | _       | _        |                                                                        |     |

| VI                     |         | _        | ace exploration using the proposed timing and energy models            |     |

|                        | VI.1    | Propo    | osed DSE flow overview                                                 | 135 |

|                        | VI.2    | DSE ι    | using high level pure analytical models                                | 140 |

|                        |         | VI.2.1   | Proposed clustering optimization approach                              | 140 |

|                        |         | VI.2.2   | Proposed mapping optimization approach                                 | 142 |

|                        | VI.3    | Demo     | nstration of the use of the DSE flow                                   | 146 |

|                        | VI.4    | DSE f    | flow evaluation                                                        | 149 |

|                        |         | VI.4.1   | Comparison of Branch & Bound-enhanced and exhaustive clus-             |     |

|                        |         |          | tering search                                                          | 149 |

|                        |         | VI.4.2   | Comparison of Branch & Bound-enhanced and exhaustive map-              |     |

|                        |         |          | ping search                                                            | 151 |

|                        |         | VI.4.3   | Use of pure analytical models for pruning                              | 153 |

|                        | VI.5    | Concl    | usion                                                                  | 154 |

|                        |         |          |                                                                        |     |

| VII                    | Cor     | nclusion | n                                                                      | 155 |

|                        | VII.1   | Synth    | esis                                                                   | 155 |

|                        | VII.2   | Identi   | fied limitations                                                       | 158 |

|                        | VII.3   | Perspe   | ectives                                                                | 158 |

|                        | VII.4   | Ouver    | ture                                                                   | 160 |

| Lis                    | t of p  | ublicat  | ions                                                                   | 160 |

| Bib                    | oliogra | aphy     |                                                                        | 163 |

| $\mathbf{A}\mathbf{p}$ | pendi   | ces      |                                                                        | 175 |

|                        | A       | Consid   | dered NN clusterings and mappings to validate our models               | 175 |

|                        | В       | Place    | and route and utilization results of the different prototype platforms | 178 |

|                        | С       | Model    | l of private memory size of tile                                       | 184 |

# List of Figures

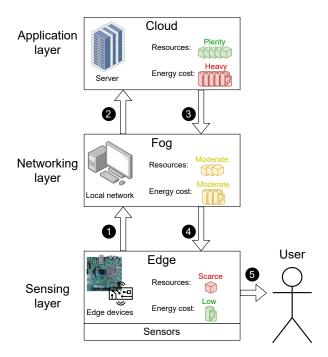

| I.1   | Typical organization of an IoT application. At the edge, data is read from sensors. Usually the data is sent through the fog to the cloud (transfers and 2), where it is processed using AI algorithms. The results of the AI algorithm are then transmitted through the fog to the edge (3 and 4) to be returned to the user (5). This figure was inspired by work presented in [17, 18].                                                                               | 30 |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

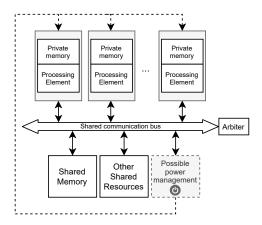

| I.2   | Schematic of generic multi-core platform architecture                                                                                                                                                                                                                                                                                                                                                                                                                    | 32 |

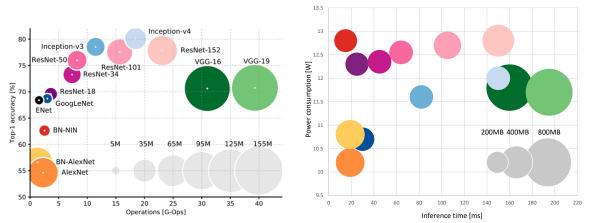

| I.3   | Plots sorting notable CNN classifier architectures from the state of the art. Graph (a) shows commonly used quantities to classify NNs. Graph (b) shows preferred quantities to classify NNs deployed onto edge devices. The data presented in this figure was obtained through the implementation and measurement of the CNNs on a NVIDIA Jetson TX1. These results come from the paper [28] (please refer to this paper for more information about the presented CNNs) | 32 |

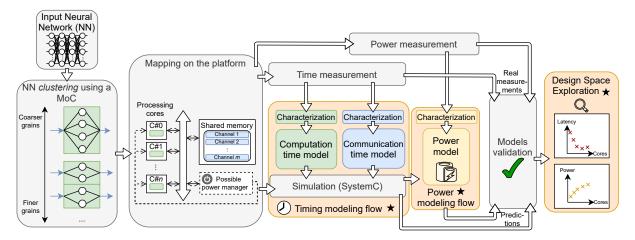

| I.4   | Proposed modeling flow for the prediction of timing and power properties of NNs deployed on multi-core platforms. The three main contributions of this work are depicted in orange                                                                                                                                                                                                                                                                                       | 36 |

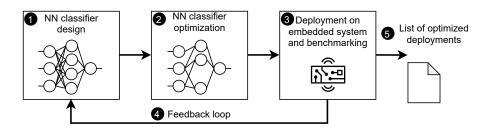

| II.1  | Diagram showing the main steps in a measurement-based approach aiming at evaluating NN deployment on embedded platforms. This diagram takes inspiration from [29]                                                                                                                                                                                                                                                                                                        | 41 |

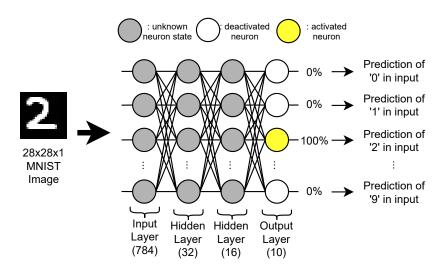

| III.1 | Example of a MLP. This NN is entirely constituted of dense layers, which are composed of a set of neurons fully connected to the previous layer. In this example, the MLP predicts that the input MNIST [11] image is a 2                                                                                                                                                                                                                                                | 54 |

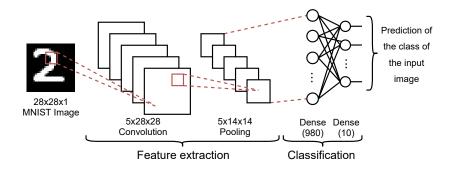

| III.2 | Example of a CNN. This NN is composed of convolution and pooling layers, used to perform feature extraction in order to ease the classification process performed by the dense layers placed afterwards                                                                                                                                                                                                                                                                  | 54 |

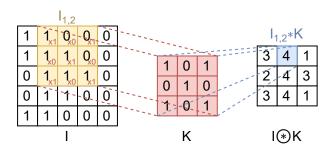

| III.3  | Illustration of the operations performed by a kernel convolution with a kernel denoted $K$ on an input image denoted $I$                                                                                                                                                                                                                                                                                                   | 56 |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

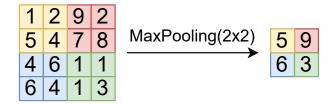

| III.4  | Illustration of the processing performed by a max pooling $2 \times 2$ layer on an input image                                                                                                                                                                                                                                                                                                                             | 57 |

| III.5  | A simple SDF graph. Actors are depicted in green whereas communication channels are depicted in blue. The element "Src" is the source of the SDF graph and the element "Snk" is the sink. Black numbers sided next to actors and hovering communication channels are the token rates of actors. The graphical notation of the SDF graph in this figure are reused identically in the rest of the figures of the manuscript | 58 |

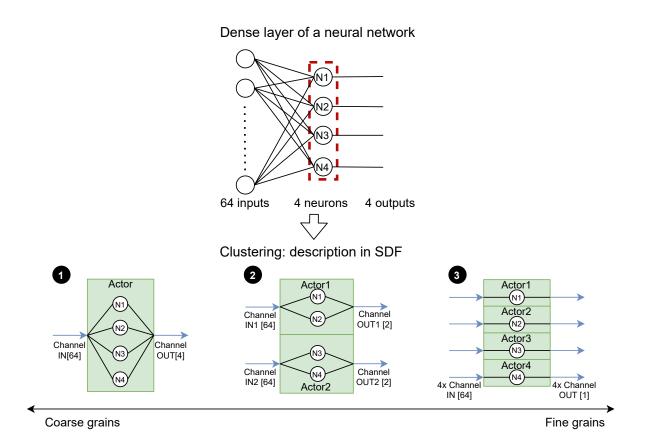

| III.6  | Three different <i>clusterings</i> of a dense layer composed of 4 neurons. ① corresponds to the coarsest granularity, as the whole layer is encapsulated into 1 actor. ③ corresponds to the finest granularity, as every neuron is encapsulated into 1 individual actor. ② corresponds to an intermediate granularity between ① and ③                                                                                      | 60 |

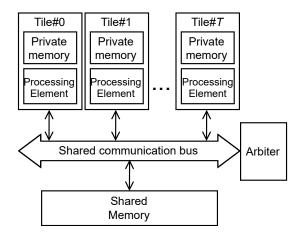

| III.7  | Example of platform which subscribes into our MoA. The MoA is composed of a set of tiles containing a single-core processor with private data and instruction memory. A shared memory is available for communications between tiles, which is accessed through a communication bus featuring an arbiter                                                                                                                    | 62 |

| III.8  | The considered versions of the platform. Version <b>1</b> features polling-based communications without the use of clock gating. Version <b>2</b> features interrupt-based communications with the use of clock gating. Automates describing the behavior of tiles when checking the availability of tokens respectively provided in <b>3</b> and <b>4</b> and examples of activity diagram in <b>5</b> and <b>6</b>       | 66 |

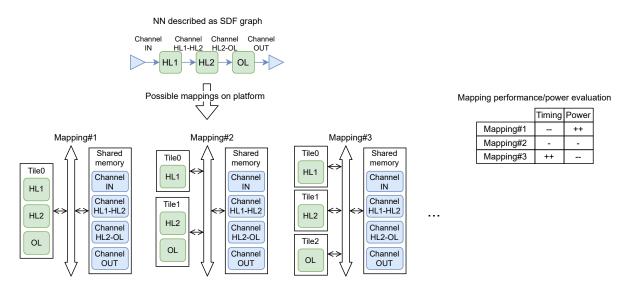

| III.9  | Three different mappings of a NN described in the SDF MoC on the considered platform                                                                                                                                                                                                                                                                                                                                       | 68 |

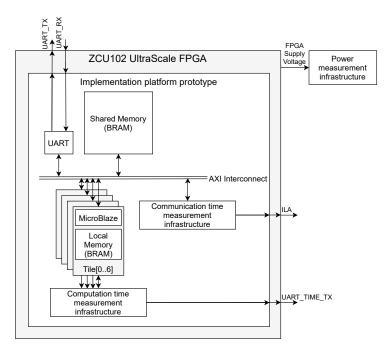

| III.10 | Block diagram of the prototype implementation platform used in this work.                                                                                                                                                                                                                                                                                                                                                  | 70 |

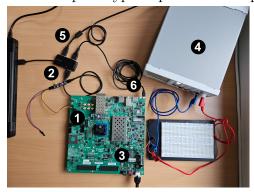

| III.11 | Experimental setup used in the scope of this thesis. The board is the ZCU102 UltraScale MPSoC+ [87].                                                                                                                                                                                                                                                                                                                                        |    |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|        | Standard Commands for Programmable Instruments (SCPI). 6 marks the connection of the board to the PC. This connection is used to program and debug the board. The UART_TX and UART_RX signals as shown in Figure III.10 are implemented on this connection                                                                                                                                                                                  | 70 |

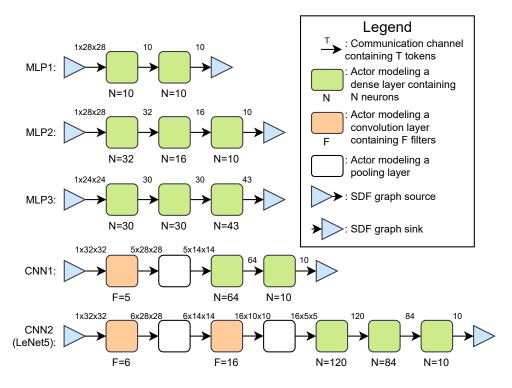

| III.12 | The considered NN applications described as SDF graphs with the coarsest level of granularity (layer grain, in which every layer's <i>clustering</i> is $C = 1$ ). We considered 3 MLPs and 1 CNN. The graphs on this figure do not feature a <i>decoder</i> actor due to the last layer's <i>clustering</i> being $C = 1$                                                                                                                  | 72 |

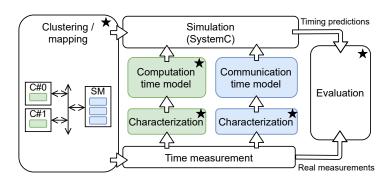

| IV.1   | Overview of the timing modeling flow. A mapping of clusterized NN onto the platform is evaluated using an executable model described in SystemC, which uses separate computation and communication time models for delay prediction. These two models are characterized through measurements. The prediction of the models are validated against real measurements. The new contributions to the flow are marked with the $\bigstar$ symbol | 76 |

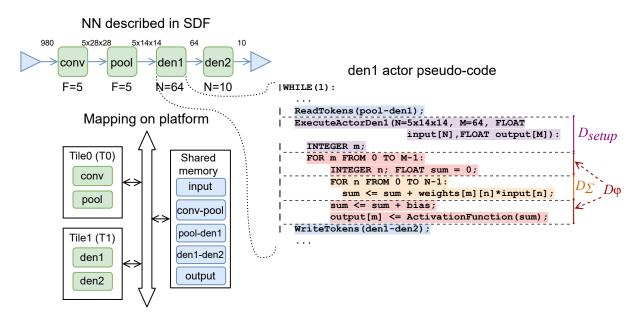

| IV.2   | Extraction of the analytical computation time model for dense layers from NNs described as SDF graphs. The pseudo-code of the dense layer $den1$ is provided. The elementary delays $D_{\Sigma}$ , $D_{\varphi}$ and $D_{setup}$ can be identified from the code                                                                                                                                                                            | 79 |

| IV.3   | Extraction of the analytical computation time model for convolution layer ers from NNs described as SDF. The pseudo-code of the convolution layer $conv$ issued from the SDF graph presented in Figure IV.2 is provided. The elementary delays $D_*$ , $D_{\varphi}$ and $D_{setup}$ can be identified from the code                                                                                                                        | 80 |

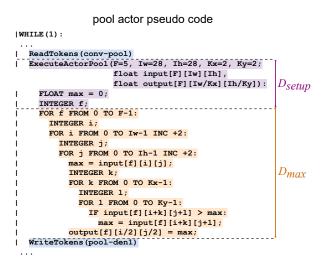

| IV.4 | Extraction of the analytical computation time model for max pooling layers from NNs described as SDF graphs. The pseudo-code of the max pooling layer $pool$ issued from the SDF graph presented in Figure IV.2 is provided. The elementary delays $D_{max}$ and $D_{setup}$ can be identified from the code                                                                                                                                                                                                                                                                                                                                                                                                              | 81 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

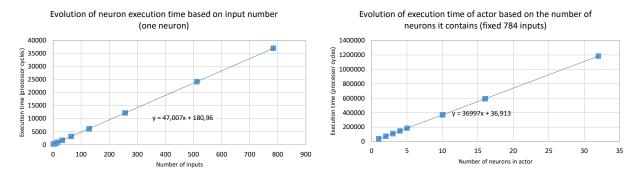

| IV.5 | Examples of plots obtained from the calibration of the analytical computation time model for dense layers. The measurements are obtained on a tile consisting of a MicroBlaze core and its private memory. The MicroBlaze code and data are stored entirely in the private memory (in compliance with the MoA). The plot on the left shows the evolution of the execution time of a neuron based on the number of inputs it has. The plot on the right shows the evolution of the execution time of an actor based on the number of neurons it contains (with a fixed number of inputs). Plots in this figure represent a subset of the tested parameters and measured data, on which multi-linear regression was applied | 82 |

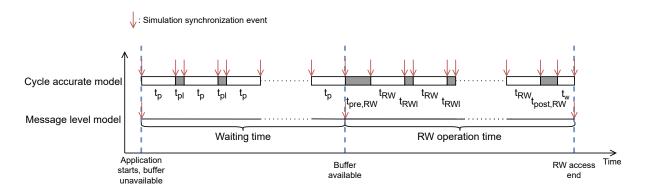

| IV.6 | Illustration of the message level communication time model from [68] compared to a transaction level model. The diagram shows the calls to the communication time model that need to be performed in order to predict the time spent by a tile to undertake a write operation of $k$ tokens on the shared memory with a waiting period                                                                                                                                                                                                                                                                                                                                                                                    | 86 |

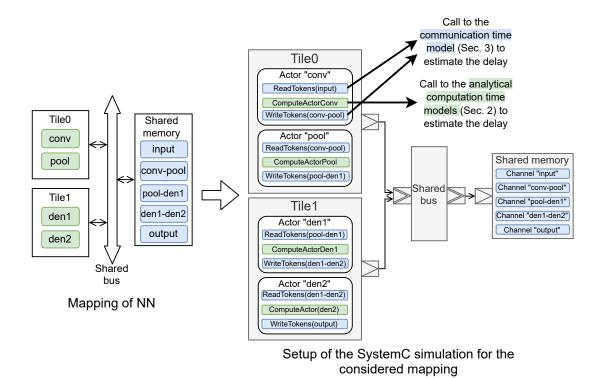

| IV.7 | Illustration of the use of the SystemC model to simulate the execution of a NN mapped onto a multi-core platform. The simulation calls the computation or communication time models based on the delay that need to be predicted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 88 |

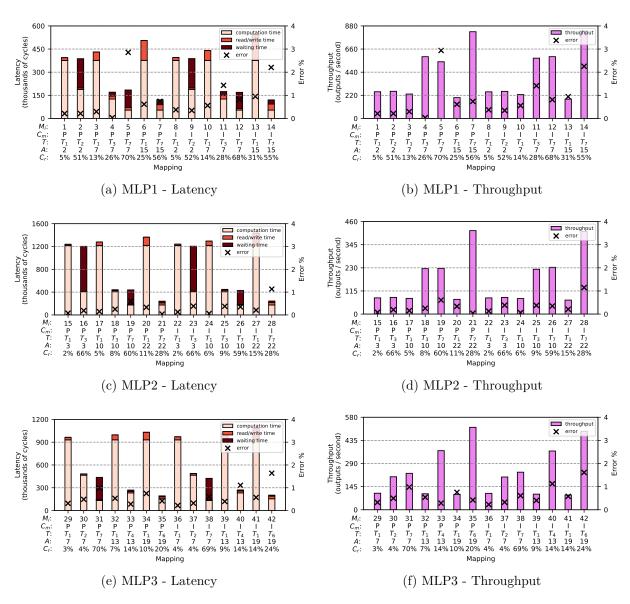

| IV.8 | Predicted end to end latency and throughput by the simulable model for the                |     |

|------|-------------------------------------------------------------------------------------------|-----|

|      | considered MLP mappings. The prediction error against measurements in                     |     |

|      | absolute and percentage is also provided for every mapping. On the plot of the            |     |

|      | latency, the $\%$ of time spent on average by cores during the execution of the           |     |

|      | application in computation, read and write and waiting phases are depicted.               |     |

|      | In X-axis, information about the tested mapping is provided: the top number               |     |

|      | $M_i$ is the mapping index, which can be used to find more information about              |     |

|      | the mapping in appendix to this manuscript. The number $C_m$ below $M_i$ is               |     |

|      | the communication mode - $P$ stands for polling, while $I$ stands for interrupt.          |     |

|      | The number of tiles used is indicated by the indice of $T$ . Then respectively            |     |

|      | the number of actors $A$ in the SDF graph and the average time spent in                   |     |

|      | communication by tiles $C_r$ (combination of read/write time and wait time)               |     |

|      | are provided                                                                              | 91  |

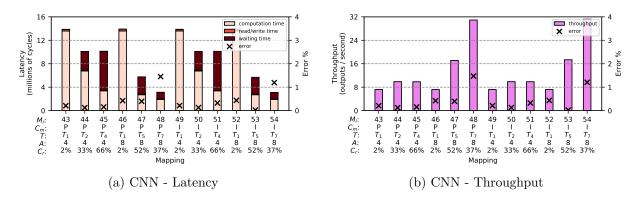

| IV.9 | Predicted end to end latency and throughput by the simulable model for the                |     |

|      | considered CNN mappings. The absolute prediction error against measure-                   |     |

|      | ments is also provided for each mapping. More information about the legend                |     |

|      | of the plots can be found in the caption of Figure IV.8                                   | 92  |

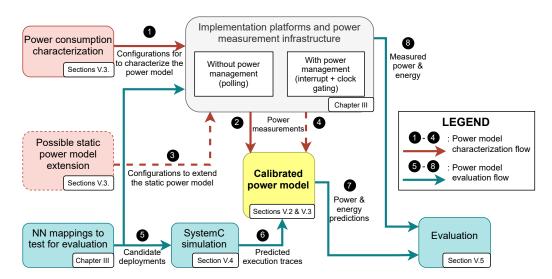

| V.1  | Overview of the methodology to obtain a power model for power and energy                  |     |

|      | prediction of NNs on multi-core platforms                                                 | 100 |

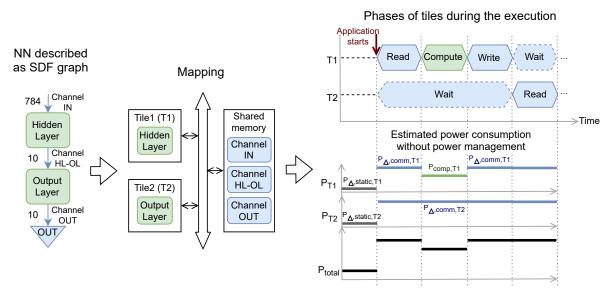

| V.2  | Estimation of power consumption in regards to the phase of tiles during the               |     |

|      | execution of NN mappings. Possible phases are: computation, read/write on                 |     |

|      | shared memory and waiting for buffer availability. The estimation of power                |     |

|      | consumption on the bottom right of the figure is provided for a platform                  |     |

|      | without power management ( $\triangle$ )                                                  | 102 |

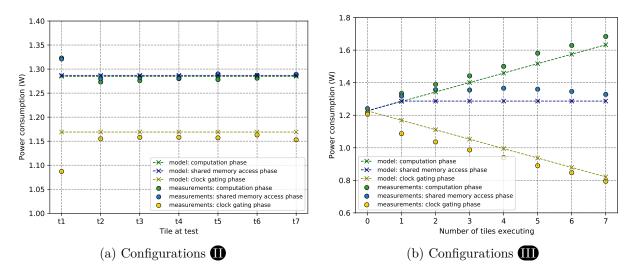

| V.3  | Extract of the measured power consumption profiles (in W) for tiles in                    |     |

|      | computation, shared memory access and clock gated phases. The provided                    |     |

|      | data include both static and dynamic power consumption. Graph (a) provides                |     |

|      | the profiles for tiles tested individually, which correspond to the configurations        |     |

|      | ① of Equation V.19. Graph (b) provides the profiles for tiles progressively               |     |

|      | enabled all together, which corresponds to the configurations marked $\blacksquare$ . The |     |

|      | configuration ① can also be seen on the graph (b): it corresponds to the static           |     |

|      | power consumption, obtained when 0 tile is executing. The reader can refer                |     |

|      | to Equation V.19 for more information on the different tested configurations.             |     |

|      | The plots also show the proposed calibrated model                                         | 115 |

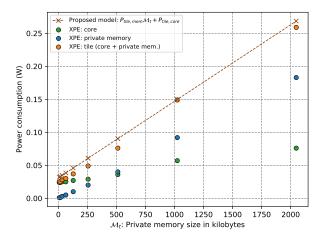

| V.4         | Extract of data gathered from XPE estimates showing the evolution of            |     |

|-------------|---------------------------------------------------------------------------------|-----|

|             | estimated power consumption of one tile based on its private memory size.       |     |

|             | The power consumption of the tile as estimated by XPE is depicted using         |     |

|             | orange dots. In orange dash lines with cross markers, our proposed model        |     |

|             | of one tile depending on its private memory size is provided. The power         |     |

|             | consumption of the core of the tile (MicroBlaze block) is depicted in green,    |     |

|             | and the interface between MicroBlaze and private memory (in blue)               | 116 |

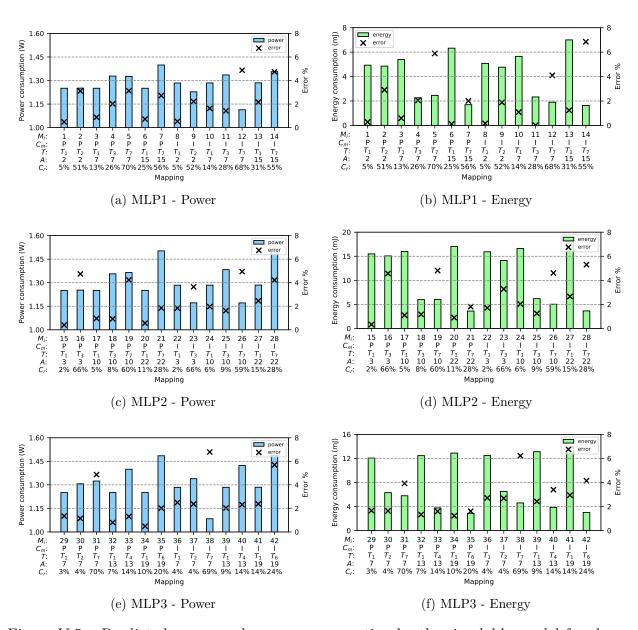

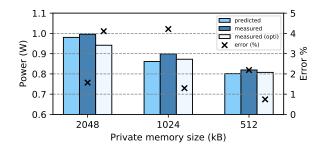

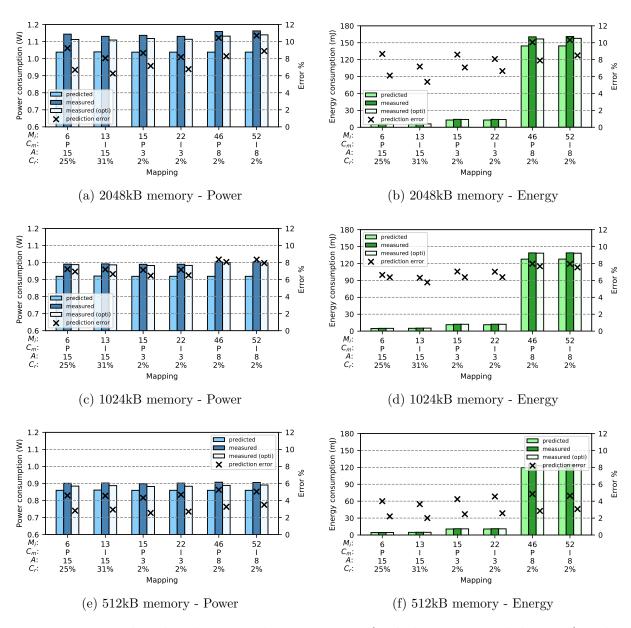

| V.5         | Predicted power and energy consumption by the simulable model for the           |     |

|             | considered MLP mappings. The prediction error in absolute value is also         |     |

|             | provided for each mapping. In X-axis, information about the tested mapping      |     |

|             | is provided: the top number $M_i$ is the mapping index, which can be used to    |     |

|             | find more information about the mapping in appendix of this thesis. The letter  |     |

|             | $C_m$ below $M_i$ is the communication mode - $P$ stands for polling (without   |     |

|             | power management), while $I$ stands for interrupt (with). The number of tiles   |     |

|             | used is indicated by the indice of $T$ . Then respectively the number of actors |     |

|             | A in the SDF graph and the average time spent in communication by tiles         |     |

|             | $C_r$ (combination of read/write time and wait time) are provided               | 121 |

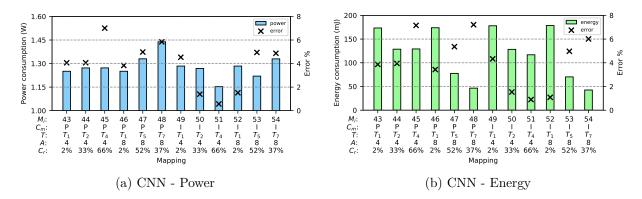

| V.6         | Predicted power and energy consumption by the simulable model for the           |     |

|             | considered CNN mappings. The absolute prediction error is also provided for     |     |

|             | each mapping. More information about the legend of the plots can be found       |     |

|             | in the caption of Figure V.5                                                    | 123 |

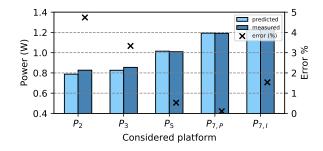

| V.7         | Predicted and measured static power consumption for the considered multi-       |     |

|             |                                                                                 | 129 |

| V.8         | Predicted and measured static power consumption for the considered single-      |     |

| , .0        | core platforms.                                                                 | 129 |

| V.9         | Predicted and measured system power (including static and dynamic) and          | 1-0 |

| <b>v</b> .0 | energy consumption for the considered mappings on multi-core platforms          | 130 |

| V.10        | Predicted and measured system power (including static and dynamic) and          | 100 |

| V.10        | energy consumption for the considered mappings on single-core platforms         | 131 |

|             | energy consumption for the considered mappings on single-core platforms         | 101 |

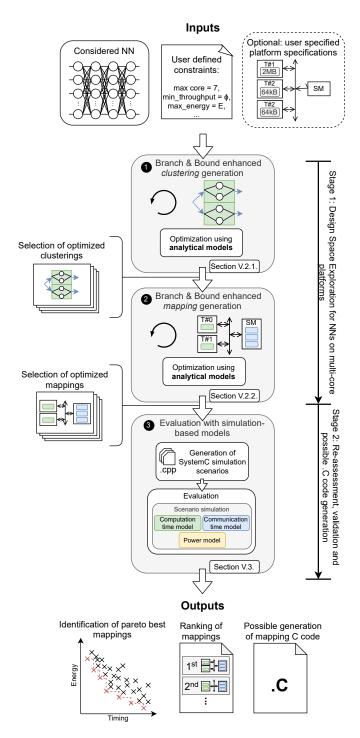

| VI.1        | Proposed DSE flow, which is organized in two main phases: first the design      |     |

|             | space is pruned using analytical models, and then selected mappings are         |     |

|             | evaluated using the simulation-based flow                                       | 137 |

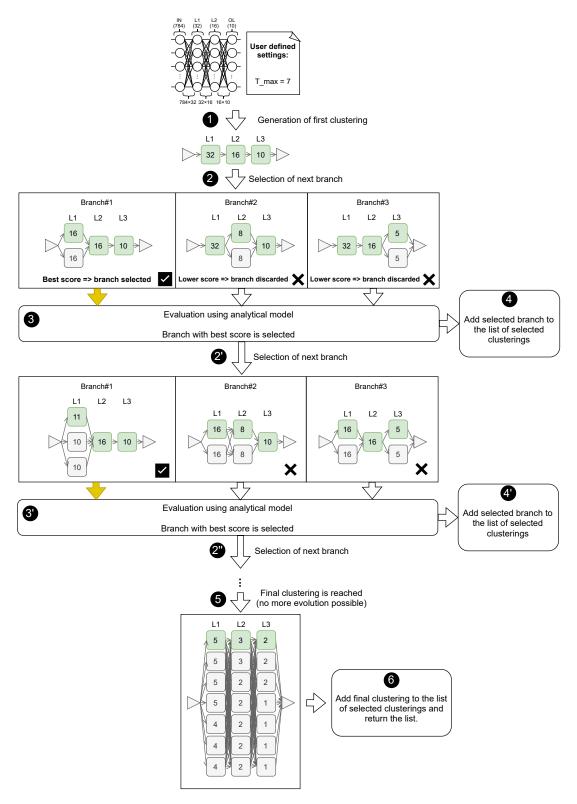

| VI.2        | Illustration of the clustering exploration process on the MLP2. The number      |     |

|             | inside actors is the number of neurons they contain                             | 141 |

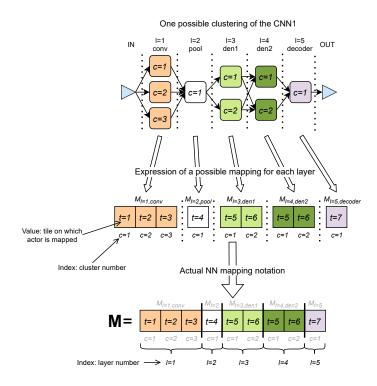

| V1.3 | CNN1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 143 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

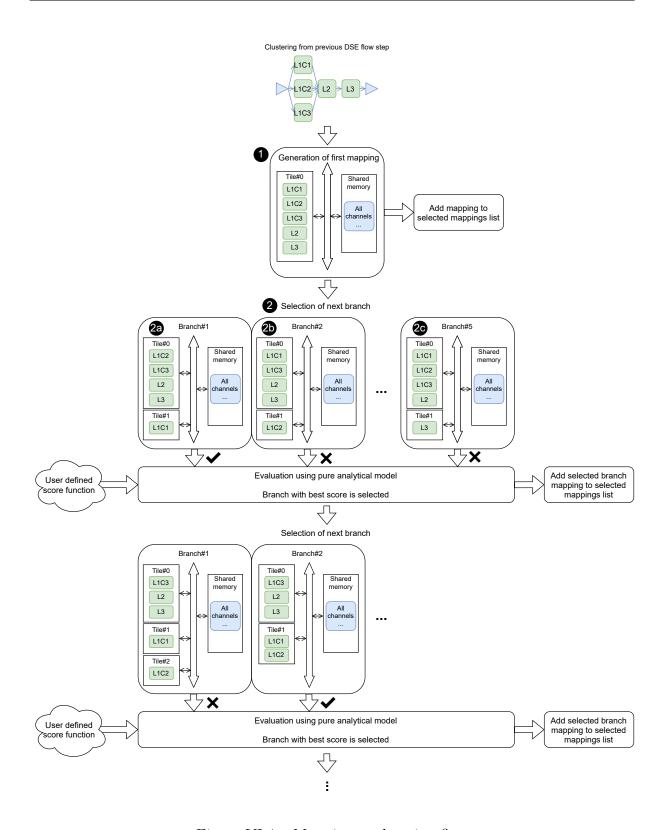

| VI.4 | Mapping exploration flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 144 |

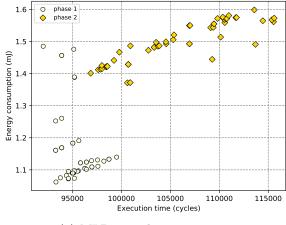

| VI.5 | Graph and table showing the highest score mappings found for the MLP1. In (a), the graph shows the predicted execution time and energy of the 50 highest ranked mappings based on the phase in the flow. As a reminder, in phase 1, pure analytical models are used, whereas in phase 2, the simulation-based evaluation flow is used. In (b), the score, encoding with respects to Figure VI.3 and communication mode of the 10 highest ranked mappings are provided. For the communication mode, P stands for polling (without power management), I stands for interrupt (with power management) | 146 |

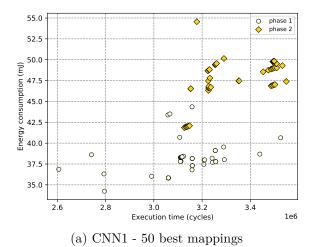

| VI.6 | Graph (a) and table (b) showing the highest score mappings found for the CNN1. Refer to the caption of Figure VI.5 for more details                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 147 |

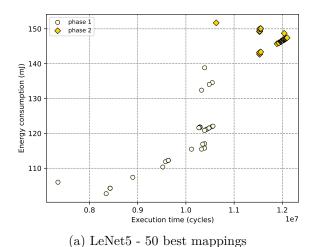

| VI.7 | Graph (a) and table (b) showing the highest score mappings found for the CNN2. Refer to the caption of Figure VI.5 for more details                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 147 |

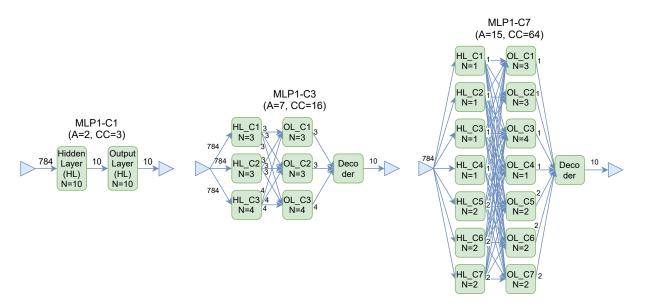

| A.1  | Illustration of the different clusterings considered for the validation of the models for MLP1. "A" corresponds to the number of actors in the clustering and "CC" to the number of communication channels. Note: due to the density of the communication channels on the clustering MLP1-C7 the number of tokens have been indicated only once for each actor (all communication channels issued by the same actor have the same number of tokens)                                                                                                                                                | 176 |

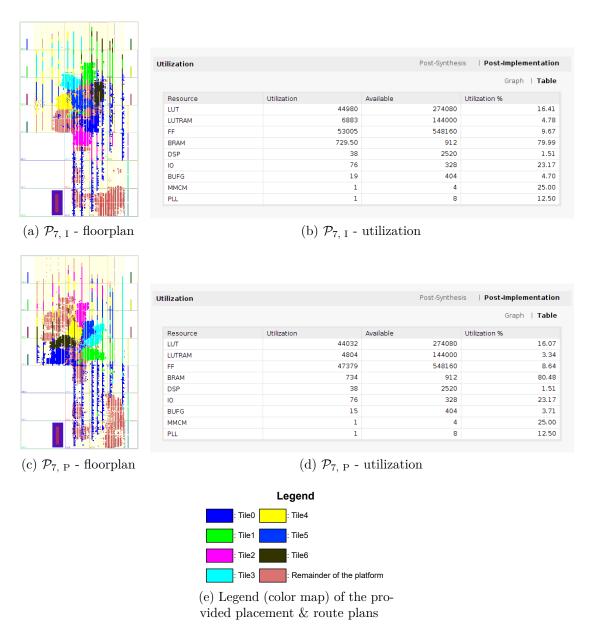

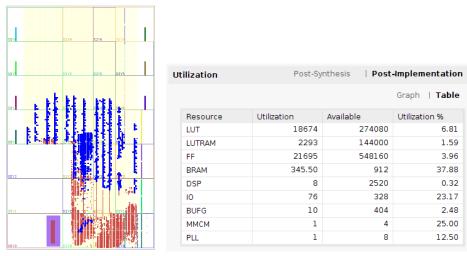

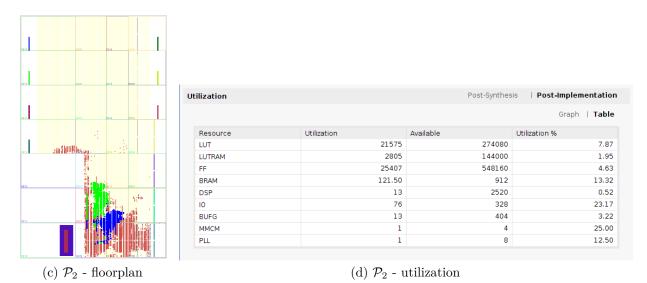

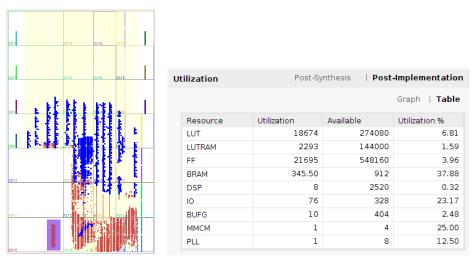

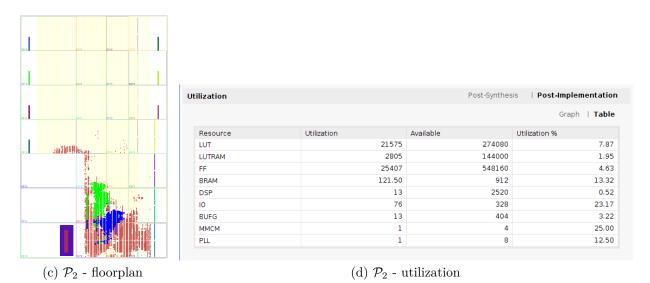

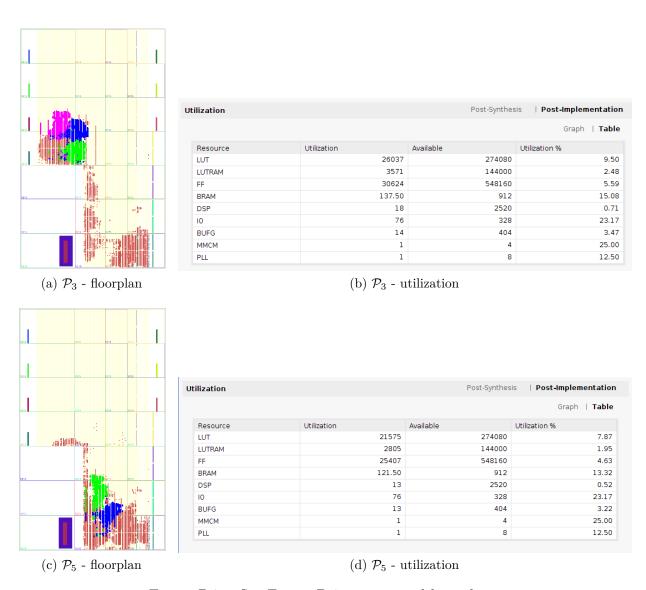

| B.2  | Place and route and utilization results of the different prototype platforms we considered for the evaluation of the power modeling flow. These platforms are used to evaluate scalability of the power modeling flow in consideration of multi-core platforms with varying sizes (in regards to number of tiles and private memory size)                                                                                                                                                                                                                                                          | 178 |

| В.3  | See Figure B.2 caption and legend                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 179 |

| B.4  | See Figure B.2 caption and legend                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 180 |

| B.5  | See Figure B.2 caption and legend                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 181 |

| B.6  | See Figure B.2 caption and legend                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 182 |

| B.7  | See Figure B.2 caption and legend.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 183 |

# List of Tables

| II.1  | Summary of main features of approaches from the state-of-the-art. In this table, evaluated quantities are provided in initials: QoS designates the Quality of Service (i.e. functional properties, and especially classifier's accuracy), T designates the timing properties (inference time, throughput), E designates the power consumption and energy, M designates memory, and A designates area (relevant for approaches using FPGAs)                                                                                                                                                                                                                                                                                           | 49 |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| III.1 | Main features of nine different multi-core platforms. When communicated by the chip provider, the core type, number of cores, core frequencies, memory sizes, communication medium and possible HW accelerator are provided in this table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 64 |

| III.2 | Number of layers, data-set and classification accuracy of the considered NNs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 71 |

| IV.1  | Calibrated elementary delays for the communication time model for polling and interrupt-based communications. All delays are in processor cycle number. The delays that differ between the two communication procedures are highlighted in bold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 87 |

| IV.2  | Observed average and maximum error against measurements on tested mappings regarding the end to end latency in processor cycles ( $\mathcal{L}$ ) and the throughput in outputs/s ( $\Phi$ ). The column titled "# tested mappings" provides the total number of different mappings tested for each application. All details about the tested mappings can be found in appendix. In this table, the mappings using polling-based and interrupt-based communications are combined. The evaluation time using the simulation flow is $\approx 20 \mathrm{s}$ when including compilation time. Without compilation time, it is in the order of tenth of seconds. The evaluation time using pure analytical models is in the order of ms | 02 |

|       | order of ms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 92 |

| IV.3 | Summary of the average and maximum prediction error on latency (in absolute value) of the simulation-based power modeling flow based on (a): the number of cores used in the mapping (b): the communication rate. Similar results are observed for throughput                                                                                                       | 94  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| V.1  | Observed average and maximum error on tested mappings regarding the power consumption in W $(P)$ and the energy consumption in mJ $(E)$ . The column titled "# tested mappings" provides the number of tested mappings. Each mapping is tested with and without power management. All details about the tested mappings can be found in appendix of this manuscript | 122 |

| V.2  | Summary of the average and maximum prediction error on power consumption of the simulation-based power modeling flow based on (a): the number of cores used in the mapping and (b): the communication rate                                                                                                                                                          |     |

| V.3  | Dimensions of the different considered platforms. The value inside the table indicate the size in kilobits of the private memory of tile. The symbol / means that this tile is not used.                                                                                                                                                                            | 128 |

| VI.1 | Number of clusterings selected by the Branch & Bound enhanced search based on their rank, with $T_{max} = 7$                                                                                                                                                                                                                                                        | 150 |

| VI.2 | Number of clusterings found by the enhanced search with Branch & Bound based on their rank with $T_{max} = 7 \dots \dots \dots \dots \dots$ .                                                                                                                                                                                                                       | 150 |

| VI.3 | Number of mappings found by the Branch & Bound-enhanced search based on their rank with $T_{max} = 3$ . The lower in the rank interval the higher the score of the mapping. E.g. mappings that belongs in the $< 1\%$ rank range have a highest score than 99% than the other mappings                                                                              | 152 |

| VI.4 | Number of mappings found by the enhanced search with Branch & Bound based on their rank with $T_{max} = 3$                                                                                                                                                                                                                                                          | 152 |

| VI.5 | Number of mappings found by the enhanced search with Branch & Bound using the simulation-based flow with $T_{max} = 3 \dots \dots \dots$ .                                                                                                                                                                                                                          | 154 |

| VI.6 | Number of mappings found by the enhanced search with Branch & Bound using the simulation-based flow with $T_{max} = 3 \dots \dots \dots$ .                                                                                                                                                                                                                          |     |

| A.1  | Considered clusterings of MLP1 for the validation of the models. The resulting clusterings are illustrated in the Figure A.1                                                                                                                                                                                                                                        | 175 |

| A.2 | Considered mappings of MLP1 for the validation of the models. The considered       |     |

|-----|------------------------------------------------------------------------------------|-----|

|     | clusterings identified based on "C_ID" are provided in Table A.1. "#T" is          |     |

|     | the number of tiles for the mapping. "M_ID" is the identifier of the mapping       |     |

|     | and "P" stands for polling-based communications whereas "I" stands for             |     |

|     | interrupt-based communications                                                     | 175 |

| A.3 | Considered clusterings of MLP2 for the validation of the models                    | 176 |

| A.4 | Considered mappings of MLP2 for the validation of the models. The considered       |     |

|     | clusterings identified based on "C_ID" are provided in Table A.3. "#T" is          |     |

|     | the number of tiles for the mapping. "M_ID" is the identifier of the mapping       |     |

|     | and "P" stands for polling-based communications whereas "I" stands for             |     |

|     | interrupt-based communications                                                     | 176 |

| A.5 | Considered clusterings of MLP3 for the validation of the models                    | 177 |

| A.6 | Considered mappings of MLP3 for the validation of the models. The considered       |     |

|     | clusterings identified based on "C_ID" are provided in Table A.5. "#T" is          |     |

|     | the number of tiles for the mapping. "M_ID" is the identifier of the mapping       |     |

|     | and "P" stands for polling-based communications whereas "I" stands for             |     |

|     | interrupt-based communications                                                     | 177 |

| A.7 | Considered clusterings of the CNN for the validation of the models                 | 177 |

| A.8 | Considered mappings of the CNN for the validation of the models. The               |     |

|     | considered clusterings identified based on "C_ID" are provided in Table A.7.       |     |

|     | $"\#T"$ is the number of tiles for the mapping. $"M\_ID"$ is the identifier of the |     |

|     | mapping and "P" stands for polling-based communications whereas "I" stands         |     |

|     | for interrupt-based communications                                                 | 177 |

| C.9 | Proposed model for private memory size needed for tile execution                   | 184 |

# RÉSUMÉ LONG

Contexte: La croissance importante du domaine de l'Internet des objets (IoT) s'accompagne du besoin d'applications reposant sur l'utilisation d'algorithmes d'Intelligence Artificielle (IA) et en particulier de Réseaux de Neurones artificiels (NNs). Habituellement, les NNs sont exécutés au niveau du cloud des applications IoT, car il contient une quantité suffisante de ressources de calcul pour permettre une exécution rapide et efficace. Toutefois, cela nécessite la transmission des données récoltées par les capteurs du niveau edge jusqu'au cloud pour le traitement. Les résultats du NN sont ensuite retransmis du cloud jusqu'à l'edge pour être communiqués à l'utilisateur de l'application. Les tendances actuelles visent plutôt à déployer les algorithmes d'IA au niveau edge en supprimant ainsi les transferts de données coûteux entre edge et cloud, permettant notamment l'amélioration du temps d'exécution et de la consommation énergétique.

Cela n'est néanmoins pas une tâche aisée, car les plates-formes embarquées disponibles au niveau edge ont des ressources de calcul et de mémoire limitées ainsi qu'un budget strict en termes de temps et d'énergie, et les NNs sont gourmands en calcul et en mémoire. Pour trouver des solutions qui optimisent les performances, l'énergie et l'utilisation des ressources, plusieurs approches d'évaluation et optimisation des NNs au niveau edge ont déjà été proposées. Beaucoup se concentrent sur le prototypage rapide, qui vise à déployer et caractériser par la mesure les déploiements de NNs sur cible réelle. Ce type d'approche requiert cependant un effort conséquent car de nombreuses solutions potentielles doivent être déployés et testés sur la plateforme cible. La technologie de mise en œuvre est également figée en raison de la nécessité d'avoir la plate-forme réelle dans la boucle, ce qui limite les possibilités en ce qui concerne l'exploration architecturale.

Pour ces raisons, d'autres approches ont été proposées, se basant sur des modèles analytiques purs qui permettent une exploration rapide et efficace des accélérateurs matériels pour les NN. Ces approches peuvent par contre difficilement être appliquées sur les plateformes multicœurs, qui sont des cibles d'implémentation privilégiées au niveau edge. Sur les plateformes multicœurs, les accès concurrents des cœurs de traitement aux ressources partagées occasionnent des contentions, qui impactent le temps d'exécution et l'énergie consommée. Pour l'exécution en pipeline des NNs sur les plates-formes multicœurs,

plusieurs aspects rendent difficile l'évaluation des propriétés non fonctionnelles :

- (1) l'expression et l'utilisation de différents parallélismes de NNs tels que le parallélisme intra- et inter-couche (pipeline) qui doivent être convenablement modélisés pour permettre l'optimisation de l'exécution.

- (2) les conflits des cœurs de traitement pour accéder aux ressources partagées telles que le bus et la mémoire qui peuvent également survenir lorsque plusieurs cœurs tentent d'y accéder simultanément, ce qui entraîne des sur-coûts importants en termes de temps et d'énergie qui doivent être correctement modélisés,

- (3) L'architecture de la plateforme : le nombre et les types de composants (cœurs, mémoire, bus, périphériques) ont un effet important sur les propriétés temporelles et la consommation d'énergie qui doit être correctement modélisé.

- (4) le comportement dynamique du système, où les cœurs exécutent différentes phases (calcul, communication) et peuvent être activés ou désactivés (par exemple via l'utilisation du clock gating).

- (5) les différentes charges de calcul/communication liées au NN d'entrée, les NNs pouvant avoir différents nombre, types et tailles de couches.

Outre les défis liés à l'évaluation, il existe un grand nombre de déploiements possibles d'un NN sur une plateforme multicœur. Les plateformes au niveau edge ont souvent de fortes contraintes de temps et d'énergie, et une exploration intensive du vaste espace de conception est donc nécessaire pour trouver des déploiements qui respectent ces contraintes. Il est nécessaire de proposer un flot automatisé d'exploration de l'espace de conception (DSE) permettant une évaluation rapide et fiable des différents déploiements, en tenant compte des enjeux susmentionnés, afin d'identifier des solutions optimisées. Ce flot doit notamment permettre de :

- (1) Trouver des déploiements optimisés de NNs sur une plateforme fixe spécifiée par l'utilisateur,

- (2) Optimiser conjointement les dimensions de la plateforme matérielle (nombre de cœurs, taille des mémoires) et le déploiement logiciel des NNs.

**Enjeux de recherche:** Le travail présenté dans le cadre de cette thèse vise à répondre aux questions de recherche suivantes :

(I) Comment fournir une évaluation rapide et précise en amont des phases de conception des propriétés temporelles et de l'énergie des déploiements de NNs sur des

- plateformes multicœurs?

- (II) Est-ce qu'une approche basée sur des modèles est plus pertinente que le prototypage rapide ?

- (III) Une approche basée sur les modèles est-elle adaptée à l'exploration rapide et fiable de l'espace de conception (DSE) des déploiements de NNs sur des plateformes multi-cœurs ?

**Proposition:** Nous présentons un flot complet de prédiction et d'optimisation des propriétés temporelles et de l'énergie qui combine plusieurs approches de modélisation. Le flot proposé permet d'optimiser l'occupation des ressources sans dégrader les performances des NNs mis en œuvre. Ces travaux permettent d'aboutir aux contributions suivantes :

- (1) Un flot de modélisation hybride pour les propriétés temporelles. Ce flot s'appuie des modèles analytiques décrivant les phases de calcul et de communication des cœurs exécutant des NNs. Ces modèles sont calibrés par la mesure et utilisés dans une simulation de haut niveau qui permet de prendre en compte les ressources partagées.

- (2) Un flot de modélisation de la puissance et de l'énergie, qui se base sur la caractérisation par la mesure et les traces d'exécution estimées par le flot de prédiction du temps.

- (3) Un flot d'Exploration de l'Espace de Conception (DSE) qui utilise des modèles analytiques de haut niveau d'abstraction pour trouver des implémentations de NNs optimisées. Le flot de modélisation proposé en (1) et (2) est ensuite utilisé pour correctement classer les solutions sélectionnées et ainsi retourner les meilleurs implémentations candidates.

Hypothèses de travail: Dans cette thèse, nous nous concentrons sur l'étude des Multi-Layer Perceptrons (MLPs) aussi appelés réseaux entièrement connectés ainsi que sur les Réseaux Neuronaux Convolutifs (CNN). Afin de faciliter le processus de déploiement, d'analyse et d'optimisation des NNs, nous les modélisons dans un Modèle de Calcul (MoC) orienté flot de données appelé Synchronous DataFlow (SDF). Nous expliquons notamment comment nous décrivons les NNs avec différents niveaux de granularité, appelés clusterings, qui définissent le nombre de groupes de neurones générés par couche du NN. Le clustering exprime le parallélisme intra-couche des NNs, permettant l'exécution des neurones en parallèles, mais occasionnant davantage de communications.

Nous utilisons un Modèle d'Architecture (MoA) basée sur des tuiles pour les plateformes multicœurs, qui comprend un nombre de tuiles défini par l'utilisateur, ainsi qu'un bus et une mémoire partagée. Le MoA peut aussi intégrer l'utilisation de gestion de la consommation par le biais du "clock gating" et l'utilisation d'un signal d'interruption. Les NNs sont programmés sur les plates-formes qui souscrivent à notre MoA en affectant aux cores les phases de calcul des neurones et les canaux de communication en mémoire. Cette étape s'appelle le mapping et elle permet d'exploiter le parallélisme intra-couche issu du clustering et également le parallélisme inter-couche (exécution en pipeline) des NNs - en mappant les différentes couches sur des cœurs différents.

Pour mener nos expériences (calibration et validation des modèles), nous avons mis au point un prototype de plateforme multicœur sur FPGA UltraScale. Cette plateforme est constituée d'un ensemble de tuiles comportant un coeur de calcul MicroBlaze et sa mémoire locale privée de données et d'instructions, d'un bus partagé AXI et d'une mémoire partagée. Cette plateforme est dotée d'une infrastructure de mesure du temps et de la puissance. Pour la validation de notre approche, nous considérons 4 NNs dont 3 MLPs aux caractéristiques différentes et 1 CNN. Nous avons testé un total de 54 mappings différents issus de ces 4 NNs.

Prédiction des propriétés temporelles: Nous présentons une méthodologie de modélisation permettant de prédire les propriétés temporelles, telles que la latence et le débit pour les NN déployés sur des plates-formes multicœurs qui respectent notre modèle d'architecture. La principale contribution de la méthodologie proposée est d'offrir des prédictions rapides et précises des propriétés temporelles en étant scalable vis à vis:

- du NN considéré en entrée,

- du clustering/mapping de ce NN,

- du nombre de tuiles utilisées,

- de la quantité de calcul/communication,

- de différentes procédures de communication (scrutage ou interruption).

Ce flot s'appuie sur des modèles analytiques décrivant les phases calculatoires et de communications sur la plateforme lors de l'exécution des NNs, sur la calibration par la mesure, et sur la simulation pour modéliser les ressources partagées. La combinaison de ces différentes approches de modélisation permet d'aboutir à un modèle hybride rapide à exécuter et offrant une grande précision et modularité. Les modèles analytiques de temps de calcul pour les NN décrivent les opérations exécutées dans les couches. Les prédictions

sont confrontées à des mesures obtenues lors de l'implémentation sur cible réelle. Pour les 54 mappings testés, les modèles proposés ont une précision de plus de 97%. Ils prennent une durée de l'ordre de la centaine de millisecondes pour évaluer un mapping. Ce temps d'évaluation monte à 20 s si on prend en compte le temps nécessaire pour compiler le modèle exécutable. Pour comparaison, nous observons que notre infrastructure de mesure automatique du temps d'exécution prend 40 s pour évaluer un mapping. Dans ce cas là, les modèles permettent un gain de temps d'un facteur 2 vis à vis d'une approche de prototypage rapide. Il est important de noter que le délai fourni pour le prototypage rapide ne prend pas en compte le temps d'entrainement du NN et génération des fichiers sources en C, de synthèse du FPGA, de génération du BSP et de compilation des librairies pour supporter l'exécution de software sur la plateforme. De même le temps de calibration des modèles n'est pas pris en compte.

Prédiction de l'énergie: Nous présentons un flot de prédiction de la puissance et de l'énergie pour les NNs déployés sur des plateformes multicœurs qui respectent notre MoA. Les modèles proposés s'appuient sur notre flot de simulation pour la prédiction des propriétés temporelles. Il est utilisé pour prédire la puissance et la consommation d'énergie en fonction des phases exécutées par les tuiles et de l'éventuelle contention des ressources. Le modèle est obtenu par une phase de caractérisation par la mesure pour offrir une modélisation précise de la consommation d'énergie dans les plateformes multi-cœurs. Notre approche de modélisation combine la simulation et la caractérisation par la mesure, ce qui permet d'obtenir un modèle scalable vis à vis du clustering, du mapping, de la charge de travail en calcul et communication ainsi que l'utilisation de stratégies de gestion de l'énergie. Le flot de prédiction de l'énergie peut être utilisé à deux fins:

- (1) Évaluer et trouver des mappings de NNs optimisés sur une plateforme multi-cœur fixe.

- (2) Optimiser conjointement les dimensions de la plateforme multicœur (nombre de tuiles, taille des mémoires) et le déploiement des NNs.

Nous présentons une étape de calibration complémentaire qui permet d'étendre l'applicabilité du modèle aux plateformes avec différents nombres de tuiles et tailles de mémoire privée, au prix d'un effort de caractérisation plus intensif. Nous évaluons notre flot de modélisation de la puissance et de l'énergie sur les 54 mappings des 4 NN considérés. Nous testons également son applicabilité sur 7 versions de plateformes différentes. Les résultats montrent que le flot permet de prédire la puissance et l'énergie avec plus de 93 %

de précision. Les prédictions sont rapides, le modèle étant implémenté sous la forme d'un script Python utilisé en post-processing du flot de modélisation des propriétés temporelles. Le temps d'exécution du script est négligeable vis à vis du temps de compilation des modèles de simulation, le temps d'évaluation restant donc de 20 s approximativement pour la prédiction du temps et de l'énergie par mapping. Le flot de prédiction des propriétés temporelles et de l'énergie que nous proposons permet de répondre aux questions de recherche (I) et (II).

Exploration de l'Espace de Conception (DSE): Nous présentons un flot de DSE permettant de chercher efficacement et d'optimiser les mappings de NNs sur les plateformes multicœurs respectant notre MoA sous des contraintes définies par l'utilisateur pour les propriétés temporelles et l'énergie. Le flot peut être utilisé de deux manières :

- (1) Rechercher des clusterings/mappings optimisés pour les NNs déployés sur une plateforme fixe spécifiée par l'utilisateur,

- (2) Optimiser conjointement la plateforme concernant le nombre de cœurs et la taille des mémoires, ainsi que l'implantation du logiciel (clustering/mapping des NNs).

L'objectif dans la mise en œuvre de ce flot est de démontrer comment des modèles à haut niveau d'abstraction peuvent être utilisés pour rapidement explorer l'espace des solutions. Le flot de DSE comprend 3 étapes:

- (1) Explorer et sélectionner les clusterings optimisés du NN considéré. Bien que le nombre de clusterings soit relativement limité, le nombre de mappings qui peuvent être générés pour chaque clustering est très grand. Une limitation du nombre de clusterings considérés est donc nécessaire. Cela est fait à l'aide de modèles analytiques rapides d'exécution et à l'aide de l'utilisation de l'algorithme de Branch & Bound.

- (2) Explorer et sélectionner les mappings optimisés pour chaque clustering. L'espace de conception des mappings est très large, cette étape est donc à nouveau menée à l'aide de modèles analytiques rapides à exécuter et de l'algorithme de Branch & Bound.

- (3) Évaluer les mappings sélectionnés à l'aide du flot de modélisation proposé basé sur la simulation. Ce dernier permet une évaluation rapide et précise des mappings, et ainsi de les classer par temps d'exécution et énergie croissants. La liste des mappings triée de cette façon est retournée à l'utilisateur. Notre flot offre également la possibilité de générer le code C permettant l'inférence des mappings sélectionnés.

Nous appliquons notre flot de DSE à 5 NNs différents et discutons les résultats. Nous comparons les résultats de notre flot vis à vis de l'exploration exhaustive pour un nombre de cœurs réduits afin d'évaluer sa capacité à trouver les mappings les plus optimisés. Les résultats mis en évidence par le flot de DSE proposé permettent de répondre à la question de recherche (III).

# **ACKNOWLEDGEMENT**

I would like to express my deepest gratitude to all those who have contributed to the completion of this doctoral thesis. This journey has been as challenging as rewarding, and I could not have succeeded without the support and encouragement of numerous individuals. First and foremost, I am profoundly grateful to my advisors at Nantes Université, Prof. Dr. Sebastien Pillement and Dr. Sebastien Le Nours, for their guidance, expertise, trust and patience throughout the entire PhD program. Their insights and feedback have been invaluable, shaping not only the content of this thesis but also my development as a researcher. I extend my sincere appreciation to Dr. Kim Grüttner, Dr. Domenik Helms, and Ralf Stemmer for their ongoing support and feedback throughout the program, and for welcoming me in Oldenburg at the German Aerospace Center (DLR). I extend my thanks to the members of my doctoral committee, Prof. Dr. Matthias Jung, Dr. Angeliki Kritikakou, Prof. Dr. Gregor Schiele and Prof. Dr. Frédéric Pétrot for their constructive criticism and insightful suggestions when reviewing my dissertation and during the PhD defense. The collaborative environment at the IETR lab and DLR has been a crucial aspect of my research experience, and I am grateful for the generosity and professionalism demonstrated by my colleagues. In particular I express my gratitude to Sandrine Charlier, Marc Brunet and Inge Kuper for their administrative and technical support.

Heartfelt appreciation goes to my father Rodolphe, my mother Sandrine, my sister Oriane, and all other members of my family for their unwavering support and understanding throughout this academic journey. Their encouragement has been a constant source of strength, and I am grateful for their belief in my abilities. Last but not least, I extend my gratitude to my great friends and colleagues, for their encouragement, camaraderie, and occasional distractions that provided much-needed breaks during intense periods of research: Rafal, Romain, (Alexis D.)<sup>2</sup>, Gaby, Gaël, Safouane, Hai Dang, May, Tamar, Guillaume, Antoine, Corentin, Nolwenn, Juliette, Reem, Fatima, Oriane, Jules, Gourav, Armel, Filippos, Magat, Katerina, Angela, Sony, Benedek, Sat, Linda, Ishan, Adrian, Avinaash, Patrick, Jan, Thomas, Bewoayia, Jannick, Rolf, Georg, Henning, Frank, Gregor, Bernd... I dedicate this work as well to all those I couldn't mention, who have contributed in one way or another to making this experience so enriching.

# INTRODUCTION

## I.1 Context

### I.1.1 Artificial Intelligence (AI) and Neural Networks (NNs)

The interest for AI has grown tremendously in the last decade. As shown in the 2023 AI Index Report published by Stanford Institute for Human Centered-AI (HAI) [1], the total number of publications on the AI topic has more than doubled since 2010. AI is a concept first introduced in 1956 [2] to designate the simulation of human intelligence in machines, allowing them to perform tasks that typically require human intelligence. Products that implement AI have become part of our daily lives, as in 2022, one-third of the US consumers owned a smart speaker [3], that integrate virtual assistants used to perform home automation actions using AI-driven key word spotting in human speech [4]. Since the 2010s, we've been experiencing the third wave of AI:

- 1. The first wave of AI took place between the 40s and 60s. In 1943, the behavior of human brain neurons was described for the first time by two psychologists in [5] as a logical model. In the late 50s, the psychologist F. Rosenblatt [6, 7] did the first hardware implementation of a single neuron called the Perceptron. Many consider the work of F. Rosenblatt as the first record in human history of a machine that implemented human-like learning process, through trial and error. This subset of AI was later called Machine Learning (ML) [8]. It includes all algorithms which are not programmed directly to solve a specific problem, but rather to learn by themselves how to solve the problem. During this first wave, AI algorithms remained however relatively simple, as it was impossible to train complex algorithms without advanced training methods.

- 2. The second wave of AI in the 80-90s was triggered by the introduction of back-propagation learning algorithm [9]. It rendered possible the adjustment of weights from all layers of Multi-Layer Perceptrons (MLPs), thus rendering the training of

more complex NNs possible. MLPs are NNs that are constituted of several layers of percetrons (aka neurons). Using this new learning approach, Y. Le Cun introduced in 1989 the first Convolutional Neural Network (CNN) [10] called LeNet. CNNs use first a set of convolution and pooling layers for extracting data from input images. The results of these layers are then passed to a MLP to classify the data. Y. Le Cun showed that CNNs could be used reliably for the recognition of hand written characters, and introduced several versions of the LeNet as well as the handwritten database MNIST [11]. However, due to the lack of computational power of hardware in this era and due to the lack of training data, more complex AI applications were still impossible.