Scaling RISC-V for Edge **Applications**

# **Edge Computing**

## The Scale4Edge ecosystem covers highly scalable components and extends them for edge applications on three levels

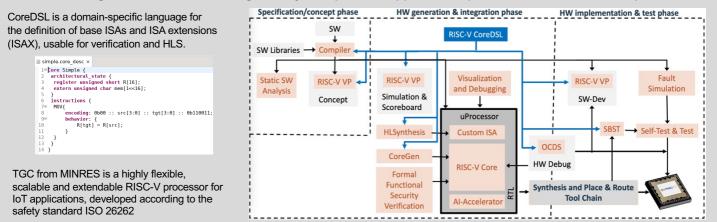

- (1) CPU instruction level defined by the RISC-V Instruction Set Architecture (ISA) and Instruction Set Architecture Extensions (ISAX)

- (2) software level defined by the C11 standard with compilers and libraries open to complementary standards like MISRA-C

- (3) operating system and firmware level through system services, configuration interfaces, and drivers

### Scale4Edge tools customize, design, verify, and produce application-specific RISC-V based microprocessors

und ISS models

and applications

### "Longnail": High-Level Synthesis for ISA Extensions

| The custom HLS                    | lowering of<br>CoreDSL | high-level SystemVerilog                                                     |

|-----------------------------------|------------------------|------------------------------------------------------------------------------|

| low is based on<br>LVM, using the |                        | DFG synthesis hw, comb, seq (CIRCT)<br>dialects (CIRCT)<br>(CIRCT) Core with |

| CIRCT framework                   | A                      | Automatic interface generator                                                |

| or generating hard-               |                        | Ecosystem                                                                    |

| vare for the ISAX.                |                        | base core                                                                    |

### Software Analysis & Synthesis

Static Software Analysis AbsInt provides 3 static analysis

tools

- Astrée analyzes C source code for runtime errors

- StackAnalyzer analyzes binary executables for worst-case stack usage

- aiT analyzes binary executables for WCET

C/C++

BOSCH

UNIVERSITAT TUBINGEN

**G**AbsInt

5)

F7I

Software Synthesis

ML Appl Signal p

AI Edge Processing Demonstrators

**TinyML** Complete end-to-end flow transforms ML model into deployable machine code including a kernel library for RISC-V MCUs (muRISCV-NN) uses and extends

- two frameworks:

- Tensor Flow Lite for Microcontrollers (TFLM) Apache TVM

## **SpiNNedge**

ML accelerator for signal processing and RNNs, applies delta encoding and sparsity exploitation

- windowing, filtering, frequency transformations

- different RNNs (GRU, LSTM, LMU)

nland-Pfälzis nische Unive

**ALTAIR**

Deutsches Zentrum für Luft- und Raumfahrt

R

P

demonstrator chip in GF 22FDX technology

## Fault Coverage and Fault Simulation FEAR-V: QEMU based framework for RISC-V register fault injection and coverage

Checker Module (VCM)

analysis with fault tracing

Stuck-at and cell-aware fault models

# Applications

## UltraTrail

Virtual Prototype Based Simulation

interpreted/compiled execution, instruction accurate

VP-VIBES: Ecosystem VP repo with peripherals

ETISS: JIT based VP with varied ISA support

customizable by plug-ins for different architectures

Software based Self-Test (SBST)

BMC-based ATPG (FreiTest) using Validity

DBT-RISE: environment to implement ISS

- Ultralow-power AI accelerator for edge devices

- · Real-time inference of temporal convolutional networks (TCNs)

- Total power consumption in the low microwatt range

### Demonstrator Chip

- Neural-network based audio event detection model

- PULPissimo-based SoC platform using IP components and software of the Scale4Edge ecosystem

- GF 22FDX technology

FPOS

SIEMENS

AROUIMEA

UNIVERSITÄT PADERBORN

SABO

UNIVERSITĂ DARMSTAD

University of Bremer

### Verification and Simulation, and Debugging

### Visualisation and Debugging

- · StarVisionPro visualizes test data, propagation of faults effects, and test coverage

- Lauterbach w/ RISC-V debug & trace solutions

#### Formal Verification for Functional Correctness and Security

Siemens EDA provides formal verification of processor cores for trojan & backdoor verification

- · GapFree guarantees relevant processor behaviors for a given ISA

- Unique Program Execution Checking (UPEC) compares two program executions to detect side channels

#### High Reliable Applications (HiRel) for space, high altitude avionics, nuclear app.

TETRISC architecture with 4 CPU cores

- different modes: high performance. distress & fault tolerant modes

- monitors for SEU, aging, temperature

- . Rad-tolerant memory protected with ECC

- based on PULPissimo plattform

- demonstrator chips in IHP130 technology

Project Management: edacentrum GmbH Andreas Vörg fon +49 511 936874-62

Project Duration: 01.05.2020 - 31.12.2023

LAUTERBACH

MINRES

Cinfineon