# Timing instructions for RISC-V based hard real time edge devices

Nithin Ravani Nanjundaswamy (<u>nithin.ravaninanjundaswamy@dlr.de</u>) DLR

This work has been developed in the ZuSE project Scale4Edge. Scale4Edge is funded by the German ministry of education and research (BMBF) (reference numbers: 16ME0122K-16ME0140). The authors are responsible for the content of this publication.

SPONSORED BY THE

Federal Ministry

of Education and Research

2022-11-07

#### 2022-11-07

## **Motivation**

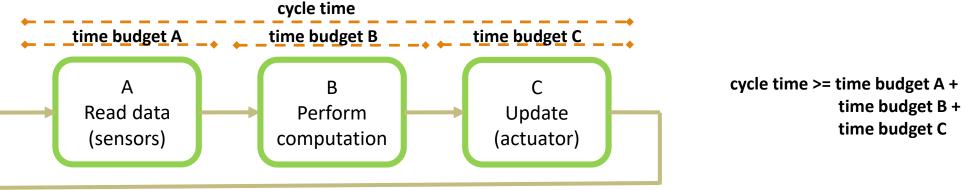

Most real-time edge devices follow cyclic execution and require precise timing and deterministic behavior

- Achieving precise timing is usually realized through software that relies on HW timers/counters, interrupts and interrupt service routines

- Hypothesis: Dedicated RISC-V custom timing instructions enable low-overhead (number of instructions) and highly precise timing (number of clock cycles) measurement and control

- Proof-of-concept: Three new instructions (measure, smonit and emonit) are implemented on Murax SoC which is based on VexRiscV core.

# Helps obtaining software execution time

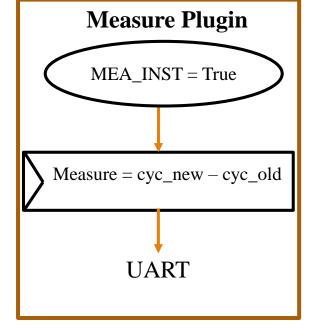

**Timing Measure Instruction**

- Counts clock cycles between successive measure

- instructions

- Measure plugin implemented in SCALA and added to Murax SoC

5th Workshop on RISC-V Activities

measure instruction is of R-type

measure;

// software to obtain

// temporal behavior

instruction 1;

instruction n;

measure;

.....

| 0000000 | 00000 | 00000 | 000    | 00000 | 0001011 |

|---------|-------|-------|--------|-------|---------|

| funct7  | rs2   | rs1   | funct3 | rd    | opcode  |

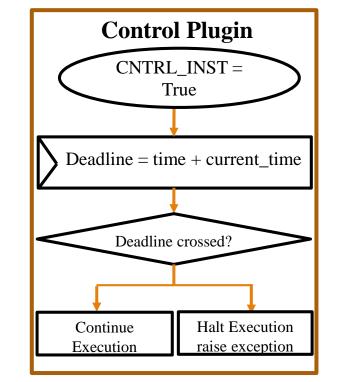

## **Timing Control Instructions**

| 0000000 | 00000 | 00001 | 010    | 00000 | 0001011 |

|---------|-------|-------|--------|-------|---------|

| funct7  | rs2   | rs1   | funct3 | rd    | opcode  |

| 0000000 | 00011 | 00001 | 011    | 00000 | 0001011 |

|---------|-------|-------|--------|-------|---------|

| funct7  | rs2   | rs1   | funct3 | rd    | opcode  |

#### Enforces a specific timing behavior

- smonit instruction (R-type)- start monitoring

- emonit instruction (R-type)- end monitoring

#### smonit(Block\_id, time);

// software to be monitored

instruction 1;

•••••

instruction n;

#### emonit(Block\_id);

- Exception raised if deadline crossed

- Nesting of control blocks is possible

## **Control Blocks Nesting**

## Nesting without overlap

smonit(1, t1);

instruction 1;

instruction 2;

smonit(2, t2);

instruction 3;

instruction 4;

emonit(2);

.....

instruction n; emonit(1);

#### **Nesting with overlap**

smonit(1, t1);

instruction 1;

instruction 2;

smonit(2, t2);

instruction 3;

instruction 4;

emonit(1);

instruction n; emonit(2);

#### Control instructions support nesting with & without overlap

## **Reference Software Solutions**

- Software solutions rely on programmable timers/counters and interrupts

- Libbla (<u>https://github.com/offis/libbla</u>)

- C++ based library originally developed for an ARM processor

- Ported to RISC-V using counter register

- Provides timing annotations to obtain temporal behavior

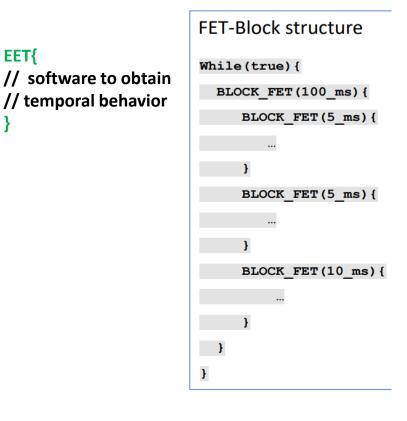

- Estimate Execution Time (EET) software counterpart for measure instruction

- Forced Execution Time (FET) software counterpart for control instructions

- C based optimized

- Mere counter to count clock cycles without OOPs concepts

EET{

## **Results, Conclusion & Outlook**

#### Hardware vs Libbla SW solution

| Measurement<br>block | Assembler code<br>overhead | Temporal<br>overhead |

|----------------------|----------------------------|----------------------|

| Hardware solution    | 7 (0.5%)                   | 20 ns                |

| Libbla solution      | 1169 (101.5%)              | 3.002 ms             |

#### Hardware Utilisation

|         | LUTs         | Registers    |

|---------|--------------|--------------|

| Measure | 189 (11.5%)  | 200 (11.97%) |

| Control | 276 (17.18%) | 225 (13.47%) |

#### Conclusion

- Precise temporal behavior with low overhead is achieved with timing instructions as compared to software approach

- ISAX comes at a cost of hardware overhead Outlook

- Can be combined with power management (slack time)

- Interface to safety and security monitoring

### Hardware vs optimized C SW solution

| Measurement<br>block | Assembler code<br>overhead | Temporal<br>overhead |

|----------------------|----------------------------|----------------------|

| Hardware solution    | 7                          | 20 ns                |

| Software solution    | 78                         | 1.89 µs              |

#### Hardware vs Software approach

Hardware solution

Software solution