Carl von Ossietzky Universität Oldenburg Fakultät II – Informatik, Wirtschafts- und Rechtswissenschaften Department für Informatik

### A hybrid RISC-V architecture supporting mixed timing-critical and high performance workloads

Bei der Fakultät II - Informatik, Wirtschafts- und Rechtswissenschaften der Carl von Ossietzky Universität Oldenburg zur Erlangung des Grades und Titels eines

#### Doktors der Ingenieurwissenschaften (Dr.-Ing.)

angenommene Dissertation

von Herrn Mehrdad Poorhosseini geboren am 06.01.1991 in Mashhad, Iran

Mehrdad Poorhosseini: A hybrid RISC-V architecture supporting mixed timing-critical and high performance workloads

Gutachter: Prof. Dr.-Ing. Wolfgang Nebel

Weiterer Gutachter: Prof. Dr.-Ing. Jan Reineke

Tag der Disputation: 13.02.2023

#### Abstract

The hardware platforms available today for embedded systems are already capable of implementing different classes of applications. These can be realtime applications, in which compliance with given time limits must be guaranteed, and high-performance applications, in which the aim is to execute as many instructions as possible per unit of time. Existing hardware platforms are usually designed and optimized for either the class of real-time applications or the class of high-performance requirements. However, if a mix of real-time and high-performance applications is to be executed on the same platform, this either causes a great deal of effort with regard to real-time verification or the platform does not meet the minimum requirements for the high-performance application.

The goal of this work is to propose a hybrid (i.e., run-time switchable) hardware platform that is capable of executing the above two classes of applications without suffering from mutually negative timing predictability and execution time optimization requirements.

This work presents a set of design requirements for such a hybrid hardware platform for embedded systems. Based on these requirements, various existing single- and multi-core platforms, ranging from high-performance embedded architectures to fully time-predictable architectures, are analyzed and compared. Based on this analysis, a new hybrid HW/SW architecture is proposed that can switch between a real-time and high-performance execution mode at runtime. In addition, this work describes the integration and implementation in an FPGA, based on an open-source RISC-V processor system and FreeRTOS as the SW management layer. Using an integrated measurement infrastructure, an analysis of software functionality, software execution timing, and switching times is performed in a single-core FPGA implementation of the proposed hybrid architecture.

#### Kurzzusammenfassung

Die heute verfügbaren Hardwareplattformen für eingebettete Systeme sind bereits in der Lage unterschiedliche Klassen von Anwendungen zu realisieren. Dies können zum einen Echtzeitanwendungen sein, bei denen die Einhaltung gegebener Zeitschranken garantiert werden muss, und zum andere Hochleistungsanwendungen, bei denen es darum geht möglichst viele Instruktionen pro Zeiteinheit auszuführen. Existierende Hardwareplattformen sind in der Regel entweder für die Klasse der Echtzeitanwendungen oder die Klasse der Hochleistungsanforderungen ausgelegt und optimiert. Soll nun aber ein Mix aus Echtzeit- und Hochleistungsanwendungen auf derselben Plattform ausgeführt werden, dann verursacht das entweder einen großen Aufwand bzgl. des Echtzeitnachweises oder die Plattform erfüllt nicht die Minimalanforderungen für die Hochleistungsanwendung.

Ziel dieser Arbeit ist es, eine hybride (d.h. zur Laufzeit umschaltbare) Hardwareplattform vorzuschlagen, die in der Lage ist, die beiden o.g. Anwendungsklassen auszuführen, ohne dass diese unter den sich wechselseitig negativ beeinflussenden Anforderungen an die Zeitvorhersagbarkeit und Ausführungszeitoptimierung leiden.

Diese Arbeit stellt eine Reihe von Designanforderungen an eine solche hybride Hardwareplattform für eingebettete Systeme vor. Basierend auf diesen Anforderungen werden verschiedene existierende Single- und Multi-Core-Plattformen, von eingebetteten Hochleistungsarchitekturen, bis hin vollständig zeitvorhersagbarer Architekturen, analysiert und miteinander verglichen. Basierend auf dieser Analyse wird eine neue hybride HW/SW-Architektur vorgeschlagen, welche zur Laufzeit zwischen einem Echtzeit- und Hochleistungsausführungsmodus umschalten kann. Zusätzlich beschreibt diese Arbeit einen Ansatz zur Integration und Implementierung in einem FPGA, basierend auf einem Open-Source RISC-V Prozessorsystems und FreeRTOS als SW-Verwaltungsschicht. Mit Hilfe einer integrierten Messinfrastruktur wird eine Analyse der Funktionalität der Software, dem Softwareausführungszeitverhalten und der Umschaltzeiten in einer Single-Core FPGA Implementierung der vorgeschlagenen hybriden Architektur durchgeführt.

#### Acknowledgement

I would like to thank my supervisor Prof. Dr.-Ing. Wolfgang Nebel for the continuous support of my Ph.D. studies and related research, for his patience, motivation, and immense knowledge. I would like to thank Dr. Kim Grüttner, in the Hardware/Software Design Methodology group of OFFIS institute, who provided detailed scientific feedback, gave me adequate research freedom, and helped me become an independent researcher. I thank Prof. Dr. Martin Georg Fränzle who was always ready for scientific discussions and interested in hearing an update on my progress. I could not have imagined a better supervision team for my Ph.D.

I would like to express my deep and sincere gratitude to Ira Wempe, who has given me suggestions, advice, and support in non-scientific works. I also want to thank Moritz Brähler, Stephan Adolf, and Razi Seyyedi for the stimulating discussions and all the fun we have had over the past four years.

I am fortunate to have family and friends who have always supported me in every decision. Thanks to my close friends who stood by me during these years: Vahid, Amir, Payam, Sasan, Danial, Iman, and Kamran. I am infinitely grateful to my parents and sister for their understanding, motivation, and all the opportunities they gave me. Last but not least, I thank my beloved wife Yasaman for her sincere love, patience, and optimism even in difficult moments; without her endless support, this dissertation would not have been possible.

# CONTENTS

| 1        | Intr | oducti                                                           | on                                                                                         | 1        |

|----------|------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------|----------|

|          | 1.1  | Motiva                                                           | ation                                                                                      | 1        |

|          | 1.2  | Scope                                                            | and Research Questions                                                                     | 2        |

|          | 1.3  | Thesis                                                           | Organization                                                                               | 4        |

| <b>2</b> | Bac  | kgrour                                                           | nd and Foundations                                                                         | <b>5</b> |

|          | 2.1  | Embe                                                             | dded systems                                                                               | 5        |

|          |      | 2.1.1                                                            | Real-time Embedded Systems                                                                 | 6        |

|          |      | 2.1.2                                                            | Timing predictability concept in an embedded system .                                      | 7        |

|          |      | 2.1.3                                                            | Worst-Case Execution Time analysis                                                         | 8        |

|          | 2.2  | Hybrid                                                           | d embedded computer architecture design $\ldots \ldots \ldots$                             | 9        |

|          |      | 2.2.1                                                            | Architectural elements                                                                     | 9        |

|          |      | 2.2.2                                                            | Requirement for hybrid switchable architecture design .                                    | 11       |

|          | 2.3  | 2.3 Overview of Fifth Generation of Reduced Instruction Set Com- |                                                                                            |          |

|          |      | puter                                                            | (RISC-V) ecosystem $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 13       |

|          |      | 2.3.1                                                            | Compilers                                                                                  | 14       |

|          |      | 2.3.2                                                            | RISC-V cores                                                                               | 15       |

| 3        | Rel  | ated W                                                           | Vork                                                                                       | 17       |

|          | 3.1  | High-I                                                           | Performance platforms                                                                      | 17       |

|          |      | 3.1.1                                                            | Ariane (CVA6) $\ldots$                                                                     | 17       |

|          |      | 3.1.2                                                            | Raspberry Pi 4                                                                             | 18       |

|          |      | 3.1.3                                                            | NVIDIA Jetson Xavier                                                                       | 18       |

|          |      | 3.1.4                                                            | Zynq 7000                                                                                  | 19       |

|          | 3.2  | Real-t                                                           | ime class platfroms                                                                        | 19       |

|          |     | 3.2.1   | $CompSoC \dots \dots$ | )        |

|----------|-----|---------|-----------------------------------------------------------------------------------------------------------------------------|----------|

|          |     | 3.2.2   | PATMOS 21                                                                                                                   | 1        |

|          |     | 3.2.3   | FlexPRET                                                                                                                    | 2        |

|          |     | 3.2.4   | SPEAR                                                                                                                       | 3        |

|          | 3.3 | Analy   | sis of suitability of existing platforms for switchable ar-                                                                 |          |

|          |     | chitec  | ture design $\ldots \ldots 24$                               | 1        |

|          | 3.4 | Gap a   | nalysis $\ldots \ldots 25$                            | 5        |

| 4        | The | esis Co | ntributions 29                                                                                                              | <b>)</b> |

|          | 4.1 | Const   | raints                                                                                                                      | )        |

|          | 4.2 | Contr   | ibutions $\ldots \ldots 30$                                  | )        |

| <b>5</b> | Cor | ncept   | 33                                                                                                                          | 3        |

|          | 5.1 | An ov   | erview of mode switchable concept                                                                                           | 3        |

|          |     | 5.1.1   | Characteristics of Real-Time mode                                                                                           | 1        |

|          |     | 5.1.2   | Characteristics of Non-Real-Time mode                                                                                       | 1        |

|          | 5.2 | Switch  | hable Architecture Model Definition                                                                                         | 1        |

|          |     | 5.2.1   | Application model                                                                                                           | 5        |

|          |     | 5.2.2   | Execution model                                                                                                             | 5        |

|          |     | 5.2.3   | Example of Application Execution                                                                                            | 3        |

|          | 5.3 | Archit  | ectural Overview of Switchable Design                                                                                       | 7        |

|          |     | 5.3.1   | Memory requirements for preparation setup 38                                                                                | 3        |

|          |     | 5.3.2   | Architectural overview                                                                                                      | )        |

|          |     | 5.3.3   | Memory hierarchy for real-time execution                                                                                    | )        |

|          |     | 5.3.4   | Memory hierarchy for non-real-time execution 41                                                                             | L        |

| 6        | Des | ign Fl  | ow and Implementation 43                                                                                                    | 3        |

|          | 6.1 | Imple   | mentation: Hardware layer                                                                                                   | 3        |

|          |     | 6.1.1   | Target implementation                                                                                                       | 1        |

|          |     | 6.1.2   | Memory system configurations                                                                                                | 3        |

|          | 6.2 | Imple   | mentation: Toolchain Layer and Linking process 47                                                                           | 7        |

|          | 6.3 | Imple   | mentation: Software layer                                                                                                   | 3        |

|          |     | 6.3.1   | Preparation setup                                                                                                           | 3        |

|          |     | 6.3.2   | Operating system support                                                                                                    | )        |

|                  |       | 6.3.3   | Realization of hybrid execution for mixed-Critical ap-                                          |     |

|------------------|-------|---------|-------------------------------------------------------------------------------------------------|-----|

|                  |       |         | plications                                                                                      | 51  |

|                  | 6.4   | Design  | n a framework for execution time measurment $\ . \ . \ .$ .                                     | 53  |

|                  | 6.5   | Summ    | nary                                                                                            | 56  |

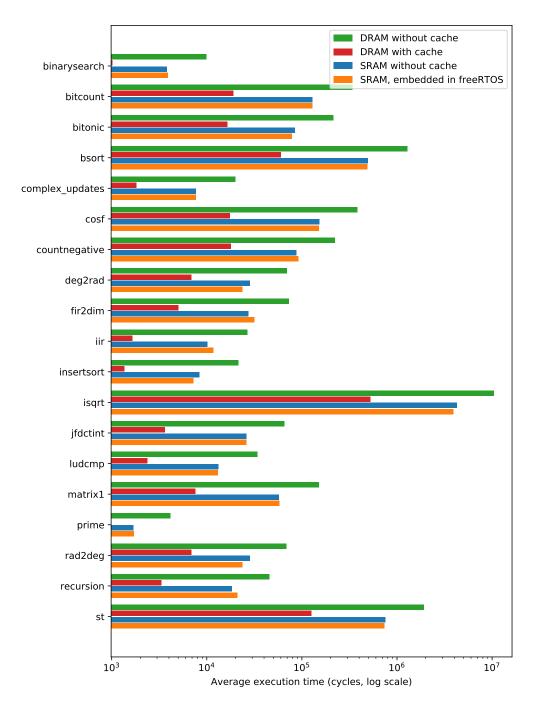

| 7                | Eva   | luatio  | n Process and Results                                                                           | 59  |

|                  | 7.1   | Evalu   | ation Setup                                                                                     | 59  |

|                  |       | 7.1.1   | TACLE benchmark Programs                                                                        | 60  |

|                  |       | 7.1.2   | Benchmark Execution process                                                                     | 60  |

|                  |       | 7.1.3   | Changes for FreeRTOS                                                                            | 62  |

|                  | 7.2   | Bench   | mark Execution on different configurations on the target                                        | 64  |

|                  |       | 7.2.1   | DRAM with cache                                                                                 | 64  |

|                  |       | 7.2.2   | DRAM without cache                                                                              | 64  |

|                  |       | 7.2.3   | SRAM without cache                                                                              | 65  |

|                  |       | 7.2.4   | SRAM embedded in FreeRTOS                                                                       | 65  |

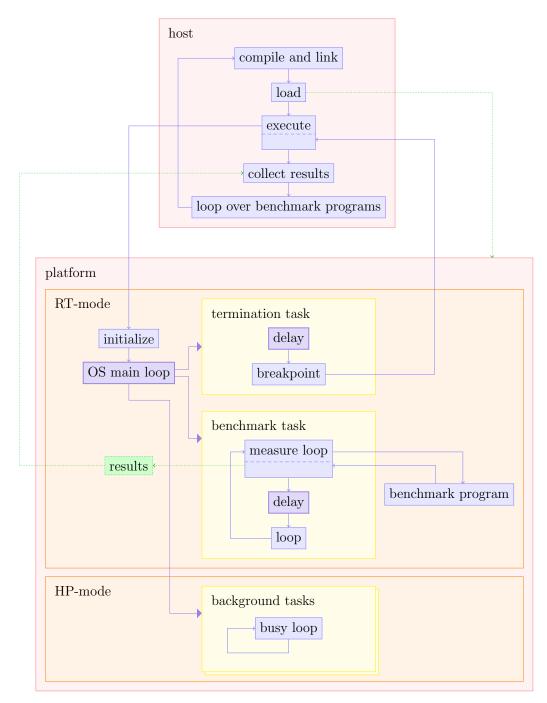

|                  | 7.3   | Result  | ts                                                                                              | 66  |

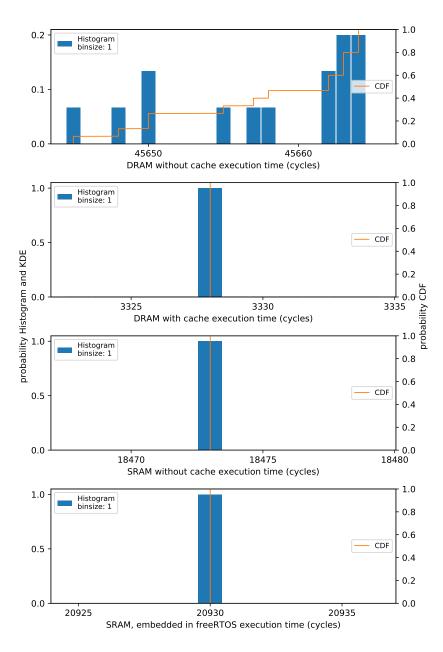

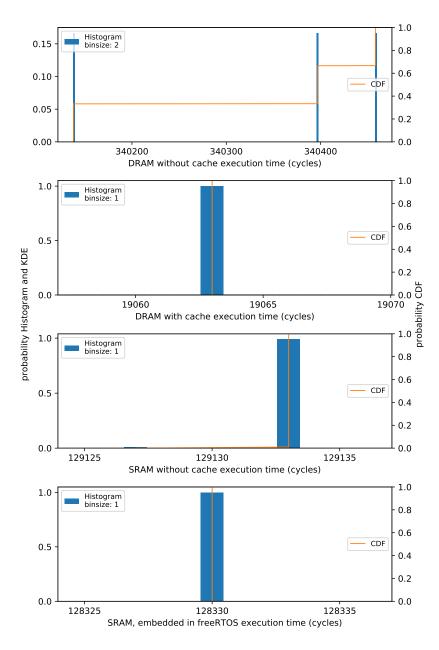

|                  |       | 7.3.1   | Average Execution Time Comparison                                                               | 66  |

|                  |       | 7.3.2   | Result interpretation                                                                           | 66  |

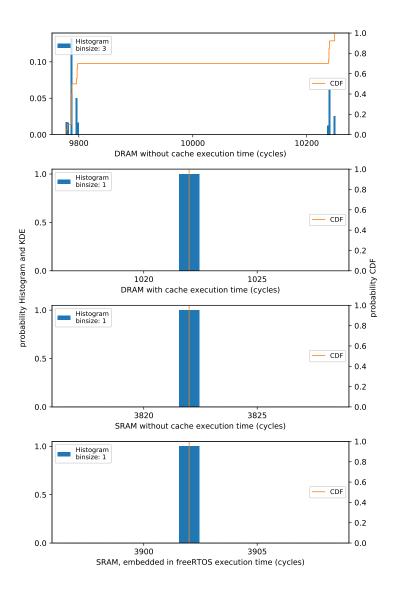

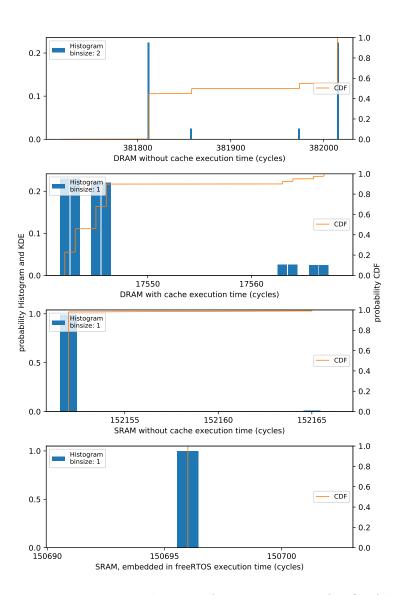

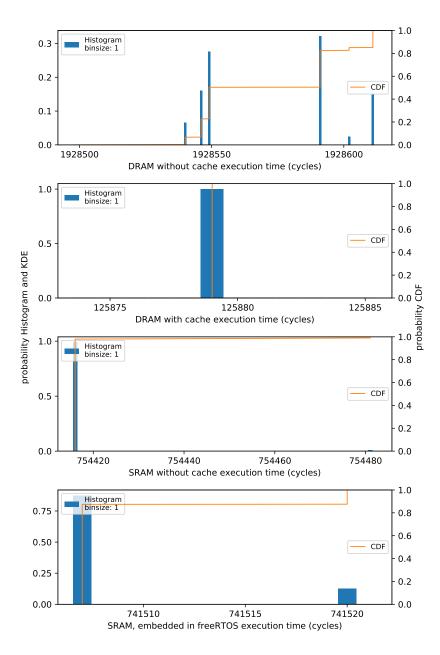

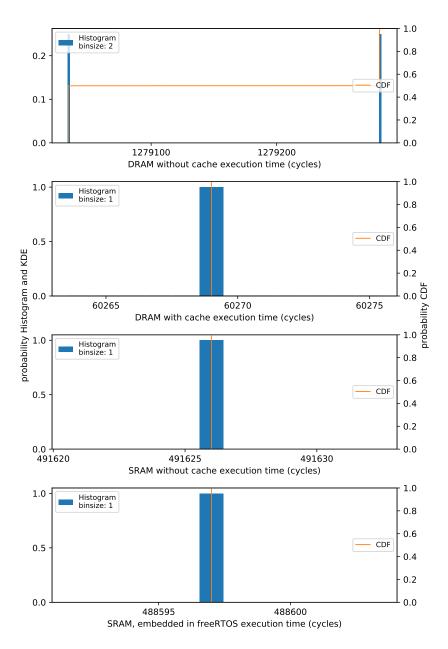

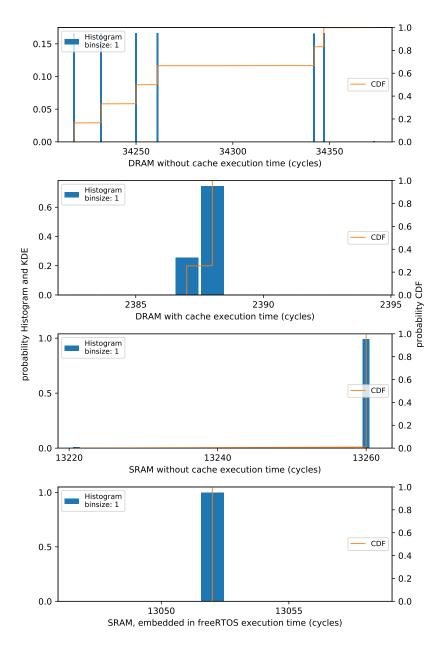

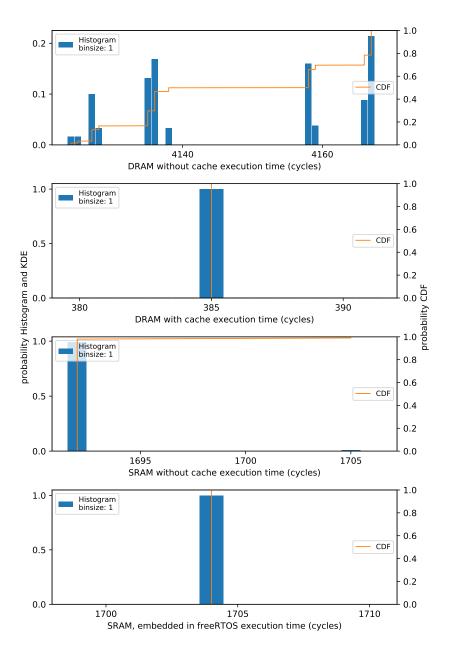

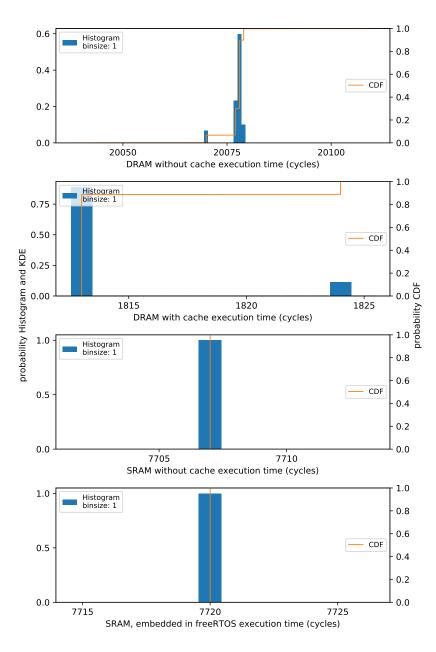

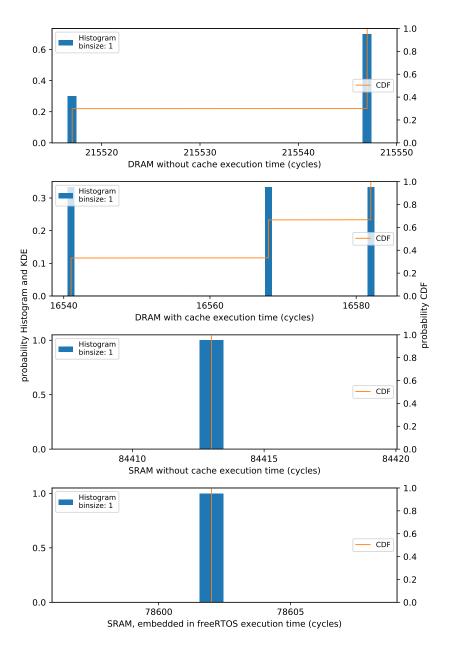

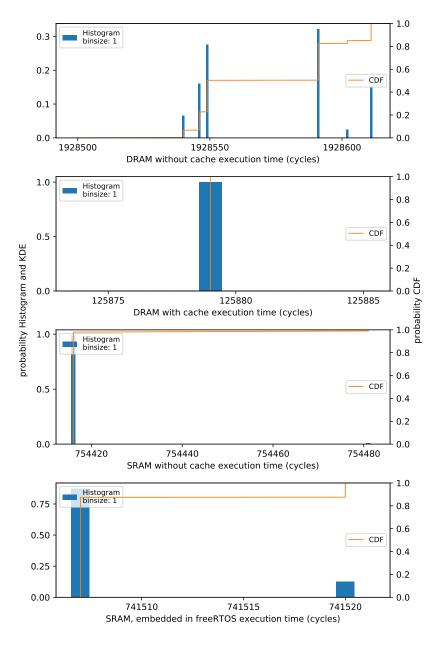

|                  |       | 7.3.3   | execution times for binary<br>search benchmark $\ . \ . \ .$ .                                  | 68  |

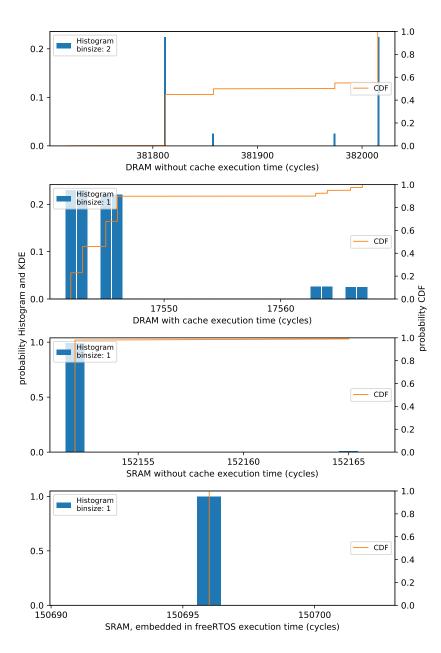

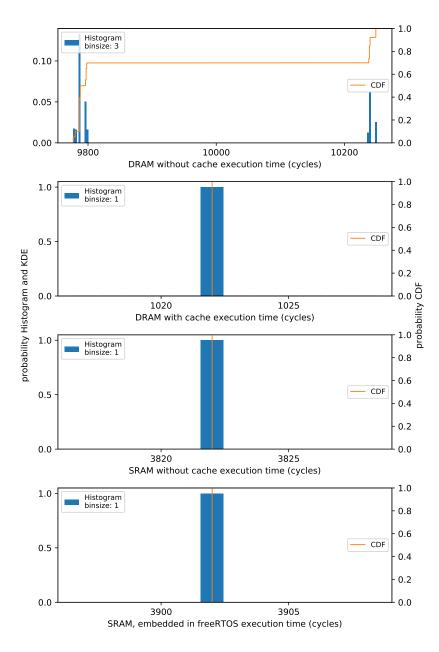

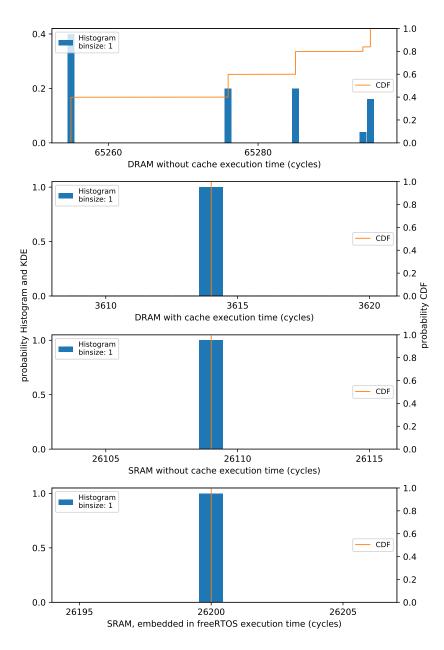

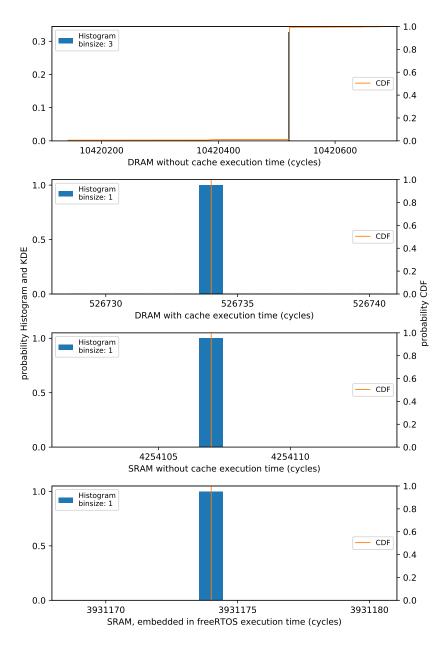

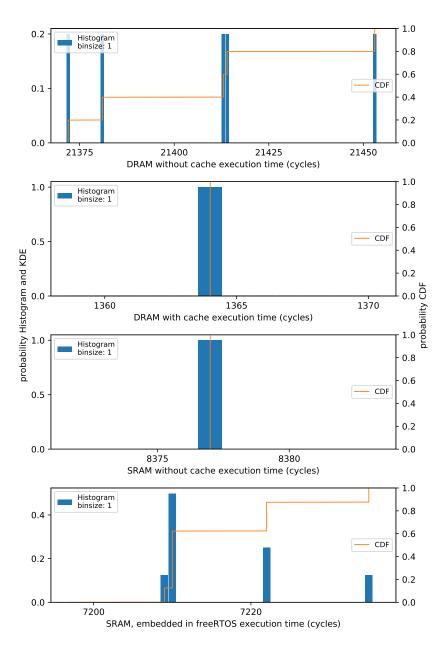

|                  |       | 7.3.4   | execution times for Cosf benchmark                                                              | 70  |

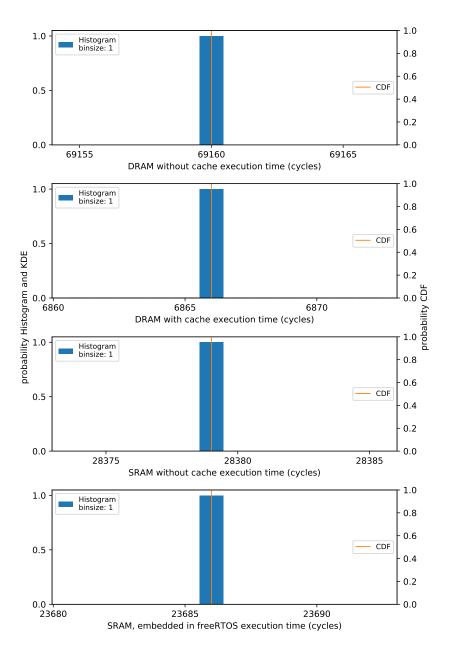

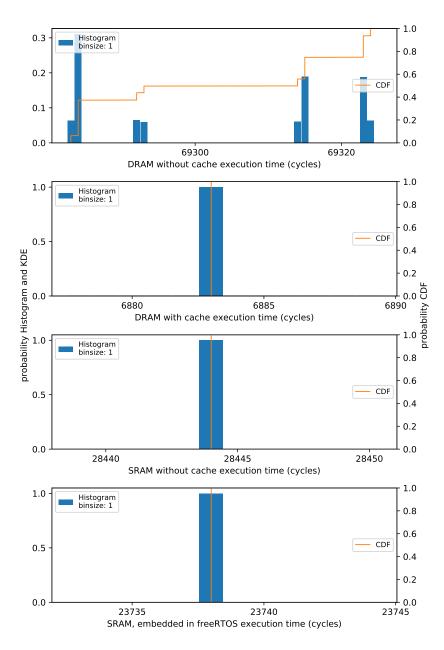

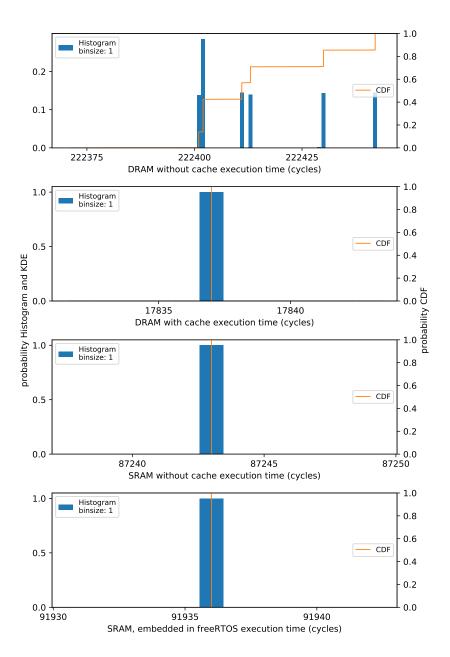

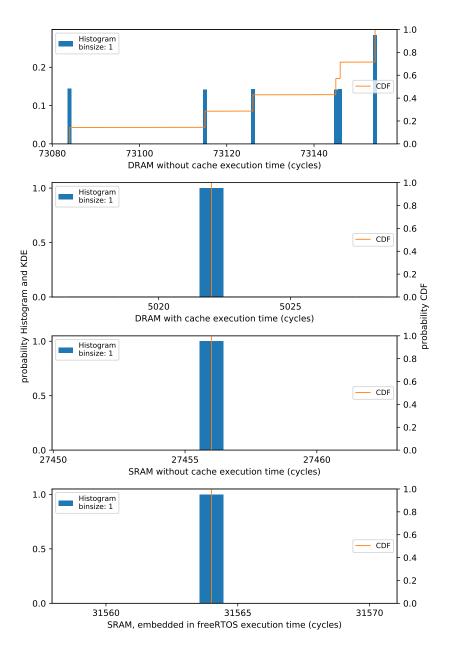

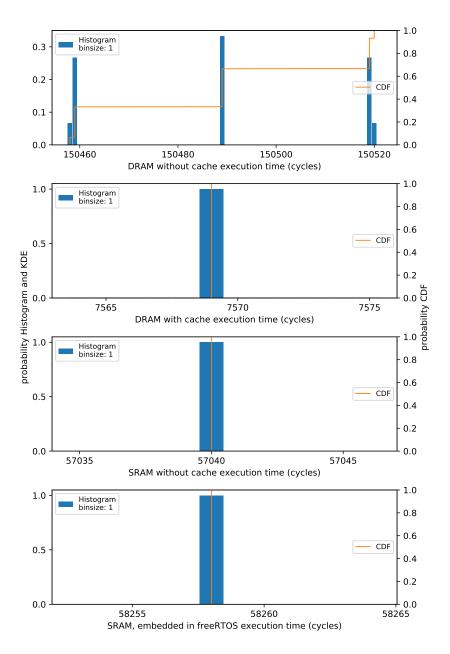

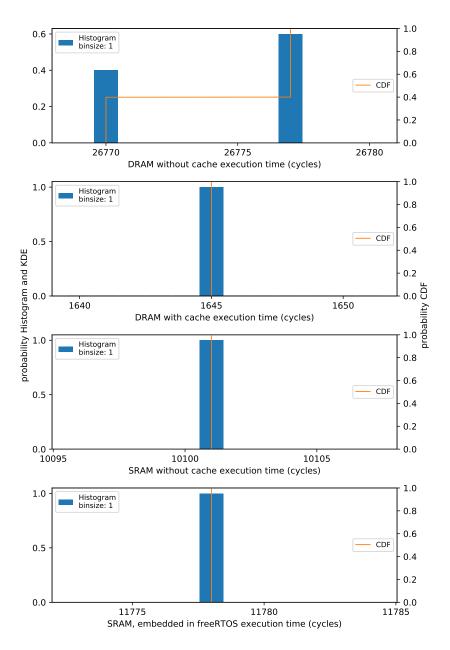

|                  |       | 7.3.5   | execution times for st benchmark $\ldots \ldots \ldots \ldots$                                  | 70  |

|                  | 7.4   | Discus  | ssion $\ldots$ | 73  |

|                  | 7.5   | Summ    | nary                                                                                            | 76  |

| 8                | Cor   | ıclusio | n and Future Work                                                                               | 77  |

|                  | 8.1   | Concl   | usion                                                                                           | 77  |

|                  | 8.2   | Future  | e work                                                                                          | 78  |

| R                | efere | nces    |                                                                                                 | 81  |

| $\mathbf{A}_{j}$ | ppen  | dices   |                                                                                                 | 89  |

| $\mathbf{A}$     | Tin   | ning C  | omparison Plots                                                                                 | 90  |

| в                | Exe   | ecution | Visualization Plots                                                                             | 110 |

|                  |       |         |                                                                                                 |     |

|                  |       |         |                                                                                                 | vii |

C Code listings

120

# LIST OF FIGURES

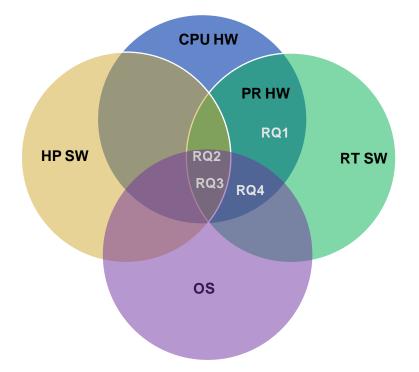

| 1.1 | Scope of this thesis                                                                                                     | 3  |

|-----|--------------------------------------------------------------------------------------------------------------------------|----|

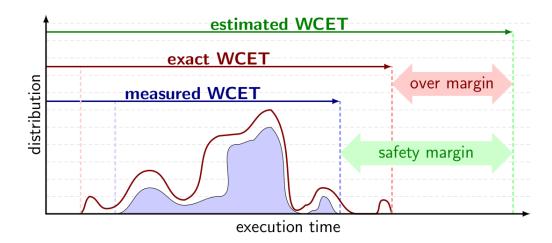

| 2.1 | Example distribution of execution time ranging from best-case to worst-case execution time (BCET/WCET)(figure from [1]). | 8  |

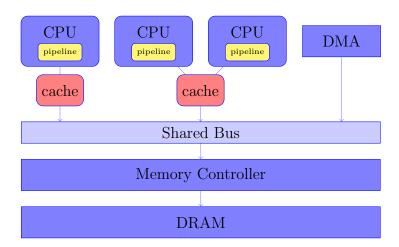

| 2.2 | Architectural elements which are essential sources of unpre-<br>dictability                                              | 12 |

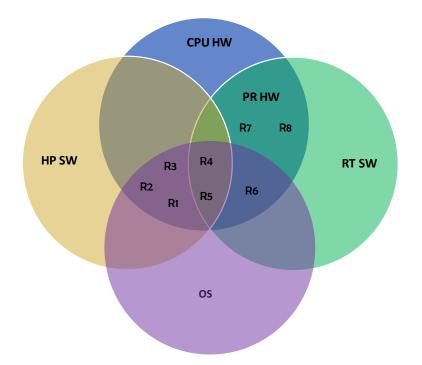

| 3.1 | Related work analysis. Mapping related work to the scope                                                                 | 27 |

| 4.1 | Contributions analysis. Mapping contributions to the scope                                                               | 32 |

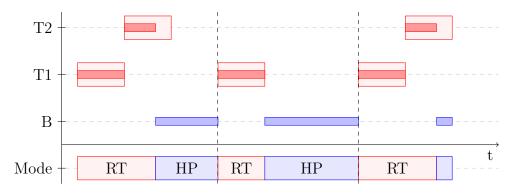

| 5.1 | Example execution trace of two execution modes representing                                                              |    |

|     | two Real-time and one Non-real-time task execution behavior                                                              | 37 |

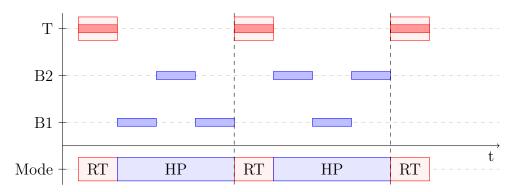

| 5.2 | Example execution trace of two execution modes representing                                                              |    |

|     | one Real-time and two Non-real-time task execution behavior                                                              | 38 |

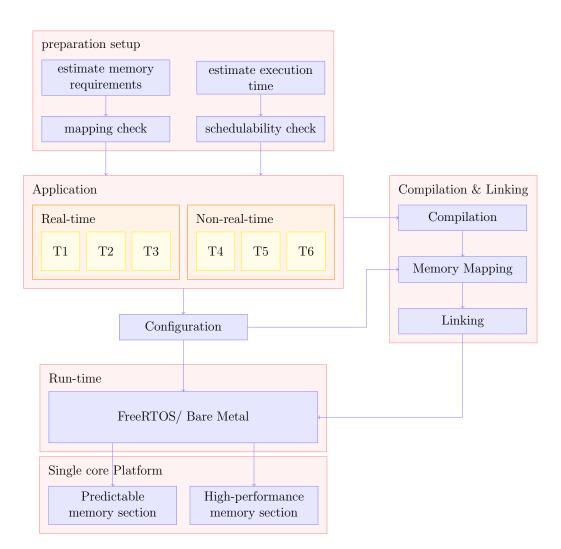

| 5.3 | Overview of the concept implementation layers on a target                                                                |    |

|     | platform                                                                                                                 | 40 |

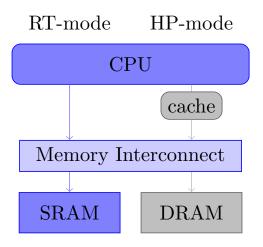

| 5.4 | Data path of the predictable memory section                                                                              | 41 |

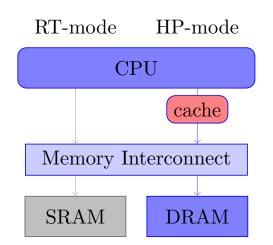

| 5.5 | Data path of the high-performance memory section                                                                         | 42 |

| 6.1 | The Genesys2 FPGA board                                                                                                  | 44 |

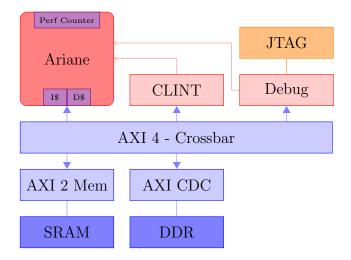

| 6.2 | Overview of the evaluation platform                                                                                      | 46 |

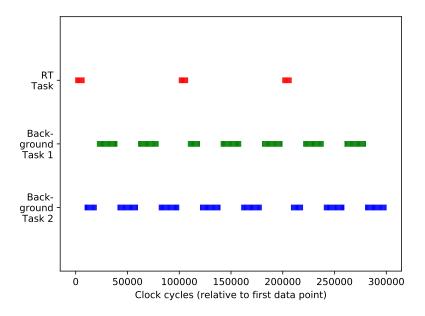

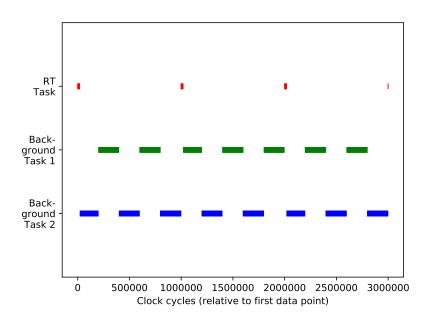

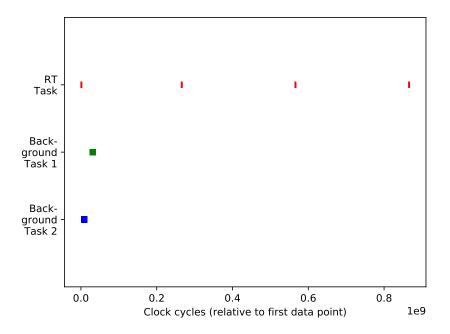

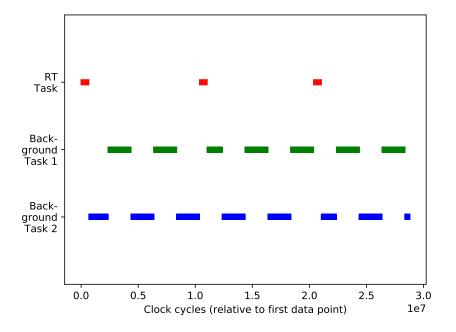

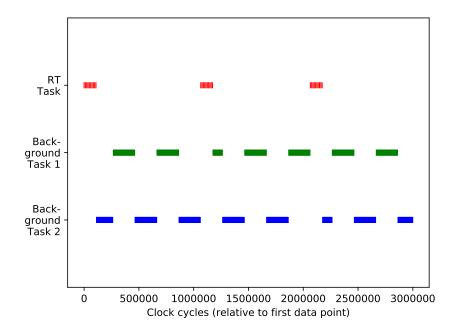

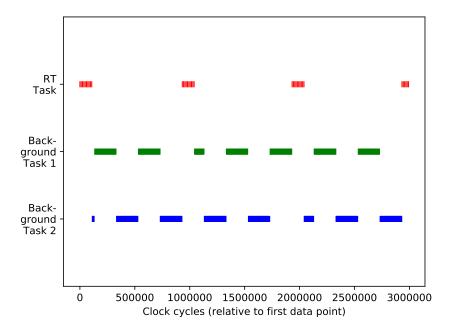

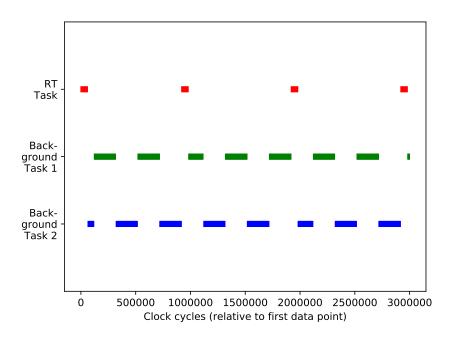

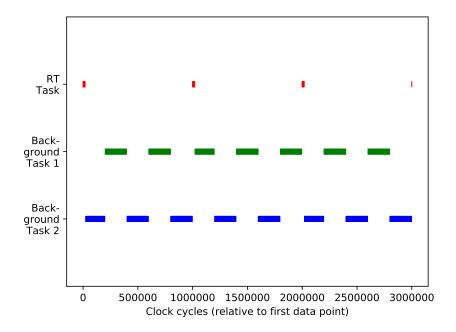

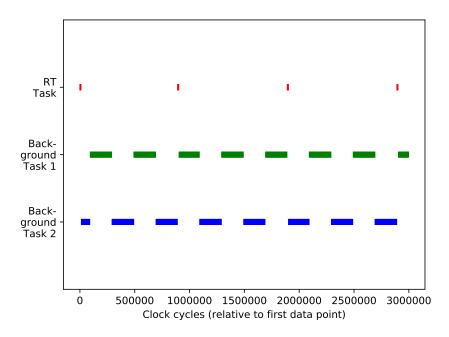

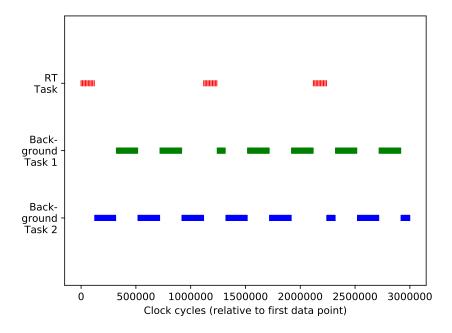

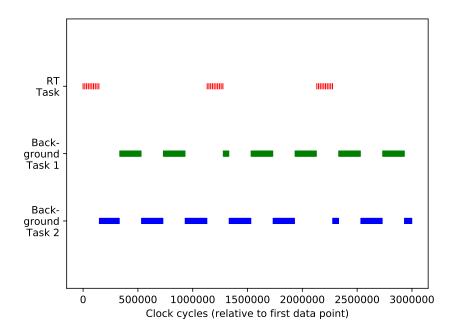

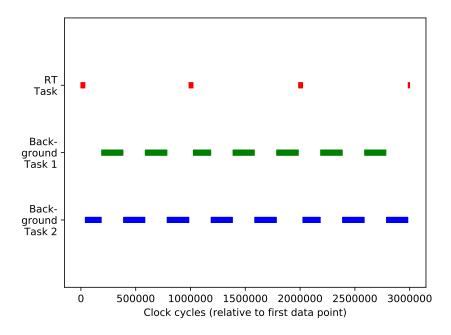

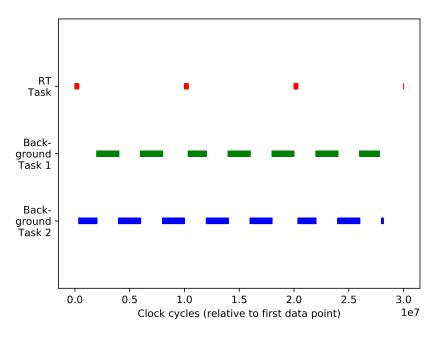

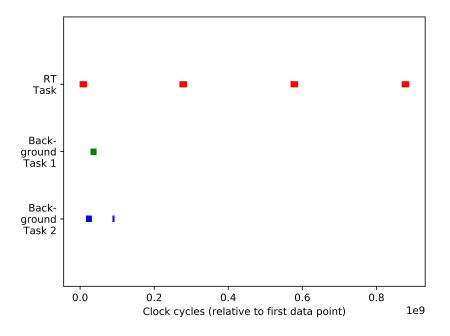

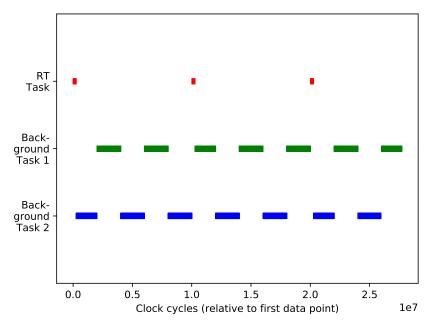

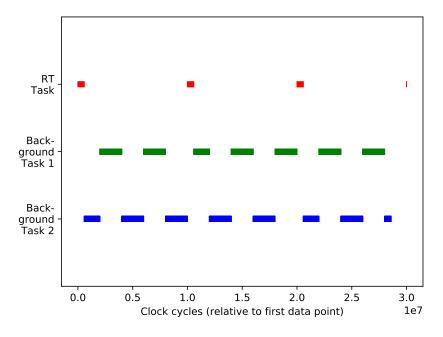

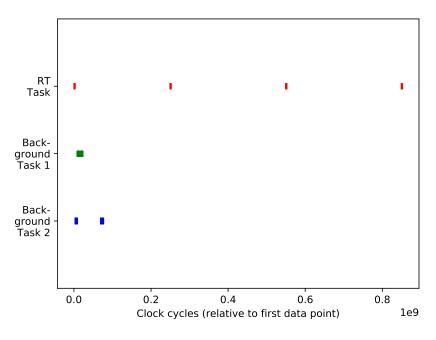

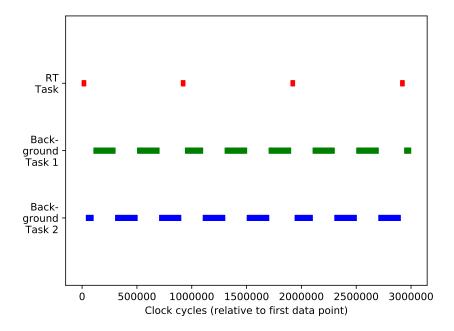

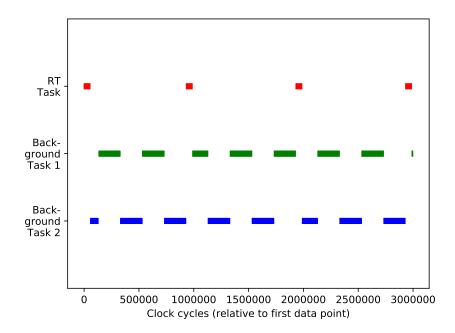

| 6.3 | Validation of mode switching in spike using two background                                                               |    |

|     | task and a periodic task $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                  | 52 |

| 6.4 | Mode switching execution time measurement with <i>binary</i> -<br>search benchmark as a periodic task                    | 52 |

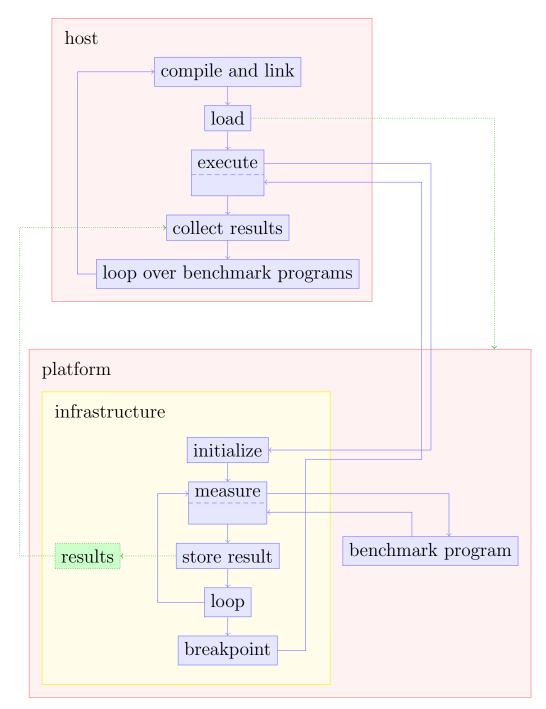

| 6.5 | Baremetal execution flow                                                                                                 | 54 |

|     |                                                                                                                          |    |

| 6.6  | FreeRTOS execution flow                                                                                                                                  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.1  | Average execution times in clock cycle for kernel benchmarks                                                                                             |

|      | of TACLE benchmark suite                                                                                                                                 |

| 7.2  | Execution time analysis on Ariane processor for binarysearch                                                                                             |

|      | benchmark                                                                                                                                                |

| 7.3  | Execution time analysis on Ariane processor for Cosf benchmark 71                                                                                        |

| 7.4  | Execution time analysis on Ariane processor for st benchmark 72                                                                                          |

| 7.5  | Comparison of proposed work with other processors in the                                                                                                 |

|      | RISC-V ecosystem                                                                                                                                         |

| A.1  | quad_bsort                                                                                                                                               |

| A.2  | quad_cosf.pdf                                                                                                                                            |

| A.3  | quad_rad2deg.pdf                                                                                                                                         |

| A.4  | quad_deg2rad.pdf                                                                                                                                         |

| A.5  | quad_ludcmp.pdf                                                                                                                                          |

| A.6  | quad_binarysearch.pdf                                                                                                                                    |

| A.7  | quad_countnegative.pdf                                                                                                                                   |

| A.8  | quad_recursion.pdf                                                                                                                                       |

| A.9  | quad_prime.pdf                                                                                                                                           |

| A.10 | $0$ quad_jfdctint.pdf                                                                                                                                    |

| A.11 | $quad_fir2dim.pdf$                                                                                                                                       |

| A.12 | $2 \text{ quad\_complex\_updates.pdf} \dots \dots$ |

| A.13 | guad_bitonic.pdf                                                                                                                                         |

| A.14 | $quad_isqrt.pdf$                                                                                                                                         |

| A.15 | $p$ quad_matrix1.pdf                                                                                                                                     |

| A.16 | $g_{\rm quad\_bitcount.pdf}$                                                                                                                             |

| A.17 | 'quad_st.pdf                                                                                                                                             |

| A.18 | g quad_insertsort.pdf                                                                                                                                    |

| A.19 | $quad_iir.pdf$                                                                                                                                           |

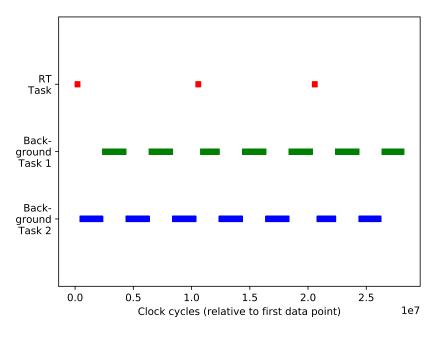

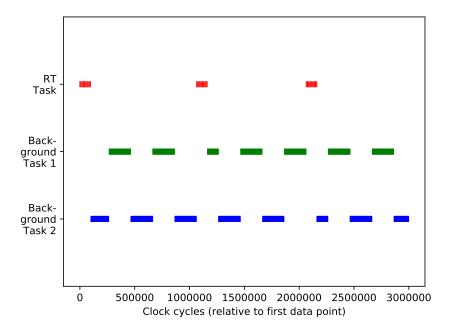

| B.1  | bsort                                                                                                                                                    |

| B.2  | cosf.pdf                                                                                                                                                 |

| B.3  | rad2deg.pdf                                                                                                                                              |

| B.4  | deg2rad.pdf $\ldots \ldots 112$ |

|------|------------------------------------------------------------------------------------------------------------------------------------------|

| B.5  | ludcmp.pdf  .  .  .  .  .  .  .  .  .                                                                                                    |

| B.6  | $binary search.pdf \ldots 113$                              |

| B.7  | $countnegative.pdf\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\$                                                                              |

| B.8  | ${\rm recursion.pdf}  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  $                                          |

| B.9  | prime.pdf                                                                                                                                |

| B.10 | jfdctint.pdf $\ldots \ldots 115$              |

| B.11 | fir2dim.pdf                                                                                                                              |

| B.12 | complex_updates.pdf $\ldots$                                                                                                             |

| B.13 | bitonic.pdf                                                                                                                              |

| B.14 | isqrt.pdf                                                                                                                                |

| B.15 | matrix1.pdf $\ldots \ldots 117$        |

| B.16 | bitcount.pdf                                                                                                                             |

| B.17 | st.pdf $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $118$                                                                       |

| B.18 | inserts<br>ort.pdf $\ldots$                                                                                                              |

| B.19 | iir.pdf                                                                                                                                  |

# LIST OF TABLES

| 2.1        | RISC-V cores from Low cost to Linux capable cores                                                                             | 16 |

|------------|-------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1        | Comparison of different processors and platforms based on the requirements of switchable architecture design                  | 25 |

| 6.1<br>6.2 | Size of static memory for different TACLE benchmarks WCET estimate for different TACLE benchmarks                             |    |

| 7.1        | Comparison of RISC-V based processors based on the require-<br>ments of switchable architecture design with the proposed work | 75 |

# LIST OF LISTINGS

| 1 | FreeRTOS initialization C code assigning static priorities to                                                                                                        |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | different tasks $\ldots \ldots 56$                                               |

| 2 | Assembler instructions for enabeling or disabeling the first                                                                                                         |

|   | level caches of the Ariane core                                                                                                                                      |

| 3 | Vivado tcl script to program the FPGA with a bitstream $\ .$ 120                                                                                                     |

| 4 | Gdb script for loading, execution and result extraction $\ldots$ . 120                                                                                               |

| 5 | Measurement instrumentation asm code for initialization the                                                                                                          |

|   | Ariane as the target platform $\ldots \ldots \ldots$ |

## Acronyms

| AXI                  | Advanced eXtensible Interface        |

|----------------------|--------------------------------------|

| BCET                 | Best-Case Execution Time             |

| CDF                  | Cumulative Distribution Function     |

| CLINT                | core level interrupt controler       |

| COTS                 | Commercially available Off-The-Shelf |

| CPS                  | Cyber-Physical System                |

| CPU                  | Central Processing Unit              |

| $\operatorname{CSR}$ | Control and Status Register          |

| DDR                  | Double Data Rate                     |

| DMA                  | Direct Memory Access                 |

| DMEM                 | Data Memory                          |

| DRAM                 | Dynamic RAM                          |

| FPGA                 | Field Programmable Gate Array        |

| FPU | Floating | Point   | Unit   |

|-----|----------|---------|--------|

|     |          | - 01110 | 0 1110 |

- GCC GNU Compiler Collection

- GPU Graphics Processing Unit

- HP High-Performance

- HPC High-Performance Computing

- HRT Hard Real-Time

- IMEM Instruction Memory

- IoT Internet of Thing

- ISA instruction set architecture

- MMU Memory Management Unit

- MPSoC Multiprocessor System on a Chip

- NoC Network-on-Chip

- OS Operating System

- PL Programmable Logic

- PREM PRedictable Execution Model

- PS Processing System

- RISC-V Fifth Generation of Reduced Instruction Set Computer

- RT Real-Time

- SDRAM Synchronous DRAM

- SPM Scratchpad Memory

- SRAM Static Random Access Memory

- SRT Soft Real-Time

- TDM Time-Division Multiplexing

- WCET Worst-Case Execution Time

### CHAPTER 1

### INTRODUCTION

This chapter provides an overview of the thesis, motivating the necessity for supporting high-performance and time-predictable embedded computing in one platform. Then the scope and research questions will be introduced. Finally, it will be explained how we cover the related contents in the rest of the thesis.

#### 1.1 MOTIVATION

In today's embedded system design, developers try to reduce cost, size, and power consumption. In order to have an efficient model in mixed-criticality systems, consisting of different tasks with different levels of assurance in one platform, we need to propose a dynamic switching between different execution modes to ease the integration of real-time and non-real-time workloads on the same system [2]. In Cyber-Physical System (CPS), where computation interacts with physical processes, the design of timing predictable architecture plays an important role because delivering the correct information to the physical world in time is essential.

We could observe that current available embedded platforms in industry and academia are mainly optimized for timing predictability or High-Performance (HP) computation. There are some reasons for these optimizations. For instance, we could consider a workload consisting of some RealTime (RT) tasks that are highly timing critical, and it should be guaranteed that RT tasks finish within the desired timing. On the other hand, we could also design a processor to meet the requirements associated with application performance, such as fast response time and processing speed. Accordingly, there is a trade-off between typical case performance and predictable systems, which means the more the design is optimized in one direction, the more we lose features in the other direction. Therefore, if we have embedded high-performance requirements, many platforms are typically available. If we have tight real-time constraints, typically, there are other platforms available, and we can separate these systems from each other. The motivation of this project is to propose an architecture that can support both of them in a single-core architecture.

#### 1.2 Scope and Research Questions

The scope of this work aims to investigate how we can get the best from both timing predictable software execution (usually supported by the simple microcontroller without cache) and high-performance software execution (usually supported by larger processors with a complex microarchitecture and several cache hierarchies). The main focus of the project is to propose a single processor architecture in the RISC-V ecosystem, which is based on a high-performance embedded processor core formerly named Ariane [3, 4] that can be switched at run-time from the high-performance to a real-time mode and vice versa. In the future, the final goal is to make this architecture applicable also in a multi-core environment.

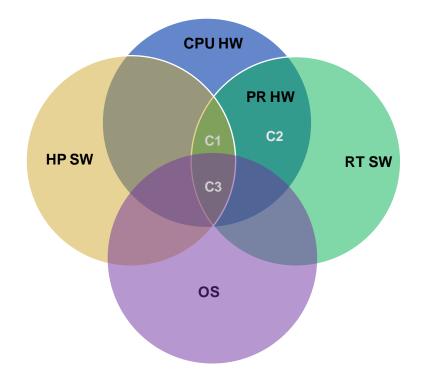

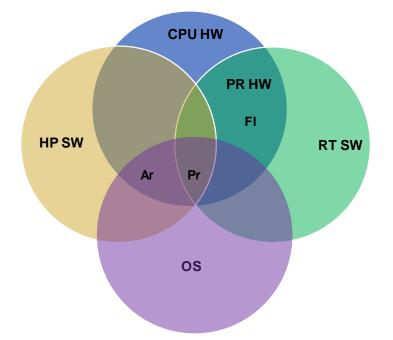

In approaching an embedded processor, this thesis will focus on improving the timing predictable execution capabilities of a high-performance embedded single-core platform. Therefore, the overall goal is to execute real-time software with minimum speed overhead compared to non-real-time software on the same hardware platform to yield predictability as much as possible. Figure 1.1 depicts the scope of this research work. We have visualized the scope using circles. So we have Central Processing Unit (CPU) on top, and predictable hardware (PR HW) belongs to the CPU as a processing part

Figure 1.1: Scope of this thesis.

for executing real-time software. We have real-time software (RT SW) and high-performance software (HP SW) on the right and left, respectively, eventually, as software support operating system (OS) on the bottom. Hence, each research question can be positioned in one of those circles or between the overlapping zones.

We formulate the following scientific questions regarding designing a switchable platform in the RISC-V ecosystem

**RQ1** What are the microarchitecture and memory subsystems that make timing predictability difficult?

**RQ2** How can timing-predictability and high-performance computation be supported on a single-core architecture by switching modes?

**RQ3** How can we benefit from an Operating System that allows switching between Real-time (RT) and High-Performance (HP) mode at runtime?

**RQ4** What overheads do these hardware and software changes have on overall execution time?

#### 1.3 THESIS ORGANIZATION

This thesis is organized into eight chapters. The second chapter provides an overview of the foundations for this thesis. Once the basics are set, Chapter 3 discusses related scientific work covering application class and real-time class processors. At the end of this chapter, the existing gap will be covered. Afterward, Chapter 4 contains the presentation of contributions and constraints. Next, in Chapter 5, the concept is presented, which starts with the application and execution model definitions. Once the model is presented, two possible example executions which could be directly extracted from the concept will be discussed. The chapter concludes with an overview of the switchable architecture design and the memory hierarchy of the concept implementation. The proposed mode switchable architecture is then implemented as described in Chapter 6. Chapter 7 of this thesis contains the evaluation of the contributions and discusses the results. Chapter 8 concludes the thesis and discusses possible future activities. Finally, Appendices presents the measurement results for all executed benchmarks.

### CHAPTER 2

### BACKGROUND AND FOUNDATIONS

This chapter includes essential information about the embedded system, the real-time embedded world, architectural elements that affect the predictability of a system, and some information about the RISC-V.

Therefore, in Section 2.1 preliminaries of embedded systems, and the connection between embedded systems and real-time computing will be explained. The timing predictability of a system and Worst-Case Execution Time (WCET) analysis as the key design requirements for real-time embedded systems are illustrated in Sections 2.1.2 and 2.1.3. Afterward, hybrid computer architecture design will be characterized by explaining the requirements that a system should meet to call a system suitable for high-performance and real-time computing. Then, we describe the RISC-V instruction set architecture (ISA) and the differences from other available ISAs. Finally, some information about available compilers and cores in the RISC-V ecosystem will complete Chapter 2.

#### 2.1 Embedded systems

Embedded systems are microprocessor-based information processing systems designed to perform certain routines of specific functions repeatedly. Embedded systems, as small and intelligent electronic systems, have become a key technological factor for complex systems as widely used, ranging from commercial electronics such as cell phones to critical infrastructures such as factory production lines and intelligence systems [5, 6, 7]. Compared to generalpurpose computers, embedded systems perform limited dedicated functions with limited computing capability and power sources. Today, around 95% of all innovations are driven and controlled by embedded electronics components and software [8]. Many of the current embedded systems are required to operate in dynamic environments, where the characteristics of the computational workload cannot consistently be predicted in advance [9].

#### 2.1.1 Real-time Embedded Systems

In general, we can classify the real-time embedded systems into two categories hard and soft real-time embedded systems. For Hard Real-Time (HRT) embedded systems, tasks must execute within a particular deadline, while in contrast, for Soft Real-Time (SRT) embedded systems, minor deadline violations will not be considered as system failure. In addition, a Scheduling policy is considered one of the main factors affecting real-time embedded systems performance. It helps to choose which task should be selected first from a queue ready to run [5]. Embedded systems that are subject to responses to the event within the precise timing constraints and predictable execution are named real-time embedded systems [10].

There are two categories of real-time tasks in real-time embedded systems. 1. Aperiodic tasks and 2. Periodic tasks. In each category, two types of tasks exist, which are: A) Preemptive: where a process "task" is blocked or interrupted by another process that has a higher priority, and B) Non-preemptive: any task completes its execution cycle even though there is another task with higher priority in the ready queue [11]. These task definitions are essential since each task could be one of the mentioned categories or subcategories in an execution flow that includes different tasks.

# 2.1.2 Timing predictability concept in an embedded system

As explained in [12], there are three different kinds of predictable systems. Simple systems with a fixed worst-case response time. In systems with only periodic tasks, the designer could choose a fixed cyclic schedule for all tasks in order to facilitate the computation. And finally, the ability to realize complex computation and react to timing relevant aspects in a pre-defined and nondeterministic way with tight and loose time constraints requires complex software scheduling algorithms. In cyber-physical real-time embedded systems, developers try to design a hardware platform that is able to integrate different levels of criticality, from highly critical workloads to high-performance workloads. However, it is challenging to design a processor that supports different levels, such as critical and non-critical workloads.

Characterizing upper and lower bounds of execution times is required to perform schedulability analysis. Therefore, a reasonable quality measure is the quotient of Best-Case Execution Time (BCET) over WCET [13]. The sources of uncertainty are the program input and the hardware state in which execution begins. Figure 2.1 illustrates the situation and displays essential notions. Accordingly, based on [14] here we can provide a formal definition of timing predictability:

**Definition 1.** (Timing Predictability). Given the uncertainty about the initial hardware states  $Q \subseteq Q$  and uncertainty about the program inputs  $I \subseteq \iota$ , the timing predictability of a program p is

$$\Pr_p(Q,I) := \min_{q_1,q_2 \in Q} \min_{i_1,i_2 \in I} \frac{T_p(q_1,i_1)}{T_p(q_2,i_2)}$$

where Q denotes the set of all hardware states and I denotes the set of all program inputs. Furthermore,  $T_p(q,i)$  be the execution time of program p starting in hardware state  $q \in Q$  with input  $i \in I$ . The quality measure quotient is  $\Pr_p \in [0,1]$ , where 1 means surely predictable.

An informal definition of timing predictability is the ability to calculate the execution time on a specific hardware platform and prove that the system

Figure 2.1: Example distribution of execution time ranging from best-case to worst-case execution time (BCET/WCET)(figure from [1]).

fulfills all requirements concerning workloads [12, 15]. In other words, a predictable execution time means that in a set of periodically repeated tasks, we could accurately predict the execution time of all tasks, regardless of how often the experiments were repeated. Therefore, running experiments with the same program under similar conditions lead to the same results. In combination with timing predictability, we require real-time analysis before using the system under consideration.

#### 2.1.3 Worst-Case Execution Time analysis

WCET analysis could be performed in many ways using different tools. Two of them are explained here:

Measurement-based WCET analysis is suitable for less time-critical software and for which the average-case behavior is more significant than a precise estimate like, for instance, in systems where the worst-case scenario is improbable to occur. The traditional and most common method in the industry to determine program timing is by measurements. The basic principle of this method follows the statement that "the processor is the best hardware model" [16]. Static WCET analysis could be performed in different phases, from flow analysis to low-level phase. There are some advantages of using static analysis techniques that rely on mathematical models, such as eliminating the need to set up a real hardware platform and calculating the safe WCET upper-bounds without running the program on the target platform. Static analysis typically uses models of all the hardware components and their arbitration policies, including CPU caches, instruction pipeline, memory bus, arbitration policies, etc. These models are typically represented in complex mathematical abstractions for which a worst-case operation can be estimated [16].

### 2.2 Hybrid embedded computer architecture design

Traditionally, High-Performance Computing (HPC) and Embedded Computing have different design, programmability, and energy efficiency objectives. However, on the one hand, due to the ever-increasing demand for performance and the need to support more robust applications - such as, e.g., smart video surveillance and, more in general, mobile and Cyber-Physical System applications - those objectives tend to adopt similar solutions [17, 18]. On the other hand, the high demands on embedded systems products put pressure on the designers to maximize the system performance and minimize the prices [19].

#### 2.2.1 Architectural elements

Single-core and multi-core devices developed using Commercially available Off-The-Shelf (COTS) components have become the preferred choice in embedded systems design. The reason is that COTS components are optimized for faster average case computation by increasing the design complexity. Nevertheless, as soon as it comes to a real-time computation where we have to meet the deadline and require a more straightforward timing analysis, these elements can cause trouble [20]. In order to improve the predictability of a COTS system, we need to replace some architectural elements by predictable versions. Some real-time researchers have proposed several solutions to improve the predictability in COTS components e.g. Pellizzoni et al. [21] introduced the PRedictable Execution Model (PREM), which enforces predictable execution for some tasks by annotating a code called by getting benefits from a compiler extension. This technique requires support from both compiler and Operating System (OS).

It is clearly evident that there is a conflict between performance and predictability. The more we achieve performance, the more we lose predictability. Here we explain the architectural elements that make predictability difficult while on the other side improve the performance.

**Pipeline:** Pipelines increase the performance of the processor by executing different instructions in parallel with little hardware cost. Hence, depending on the employed pipeline features, the complexity of WCET analysis varies. For example, dynamic branch prediction and deeper pipeline design bring about more dependencies and influence both execution time and nondeterminism in terms of predictability.

Cache hierarchy (L1 and L2): Analysis of modern caches which designed for high-performance multi-core systems is extremely challenging due to the replacement policy and high set-associativity. It is necessary to determine the cache latencies, but usually, the latency provided by companies like ARM and Intel could not be used to guarantee WCET tight estimates because these latencies are more for best or average cases.

Scratchpad Memory (SPM): In [22] a Dynamic Scratchpad Memory (SPM) unit has been introduced in order to protect the critical tasks from interference of non-critical tasks. Any task that runs out of the SPM is guaranteed to have a predictable execution time. On the other hand, because the non-critical tasks run out of the cache, there is no degrading in the performance of other non-critical tasks.

Shared bus: Multiple cores access the main memory via a bus. The impact of bus arbitration protocol and communication delay must be accounted for to obtain a tight WCET analysis. One solution is the TDMA bus arbitration which is an excellent mechanism to isolate the tasks and is

predictable and composable. However, most of the existing high-performance COTS-based systems did not apply the TDMA, mainly because it requires additional hardware modifications.

**DRAM memory:** The unpredictability in DRAMs originate from their internal architecture, which is designed to deliver high volume storage at low cost. The target row must first be opened on a DRAM access before reading, or writing operations can be issued to the word-sized column elements. The response time of memory requests in DRAM is highly variable because a single DRAM chip is designed to have a limited data bus (usually 8 bits) to minimize chip cost [23]. So, this impacts the execution time from a few clock cycles to tens of cycles. Therefore, DRAM memories should be considered a highly unpredictable resource.

**Memory Controller:** The memory controller connects the processor tile to the off-chip DRAM and is responsible for scheduling memory accesses according to the system requirements. Thus, the response time to a memory request strongly depends on the page policy, the scheduling algorithm, and the power-management policy used in the memory controller.

**Direct Memory Access (DMA):** In many embedded systems, whenever a task requires to communicate with an off-chip memory, DMA allows this access independently from the processor. This feature is useful for decreasing the CPU overhead, leading to better performance at the end. However, the composition of DMA with other components, for instance, simultaneously accessing a bus, can make the predictability difficult [24].

#### 2.2.2 Requirement for hybrid switchable architecture design

From the perspective of the architectural elements, some characteristics make a system suitable for predictable or high-performance computation. These characteristics could be related to either the processor core or the whole platform. Our analysis focuses on identifying the suitability of different platforms for the realization of implementing a switchable architecture between high-performance and real-time modes. There are some constraints that our

Figure 2.2: Architectural elements which are essential sources of unpredictability.

desired system should meet for building a switchable architecture. These constraints could be identified as specific requirements for the switchable architecture.

**Reproducible and predictable execution times:** In order to fulfill this requirement, both processors and the memory subsystems directly connected to the core need to be time-predictable. In this regard, static execution time analysis is required to estimate the WCET to guarantee that execution is free of interferences. For instance, a compiler can increase the predictability by annotating metadata to the binary file of critical applications so that these applications execute e.g. from the scratchpad memory, to omit the impact of the Dynamic RAM (DRAM) for hard real-time workloads.

**Reproducible and predictable communication times:** In a singlecore scenario, it is not a big problem, but as soon as we have DMA, it can be problematic whenever some master components want to access the bus simultaneously. Here we are interested in evaluating the predictability of components like busses that are being used to safely upper bound the communication times of the shared resources. A critical decision here is which kind of memory controller each platform uses and how DRAM accesses are managed in the scope of predictability. Some types of memory controllers could significantly enhance predictability. Operating system capability to support task scheduling for mixed-criticality workloads: Here the task scheduler has to figure out the sequence of programs while keeping specific timing constraints. In this regard, the predictability of a platform helps a lot to provide the scheduling guarantee because, without it, there is no guarantee for all times. Thus, in some cases, it turns out to be operating system support for real-time systems to handle the execution of hard real-time and soft real-time tasks. Time-Division Multiplexing (TDM) is a common solution for mixed workloads, but this method's problem is higher latency.

**High-performance features:** This can be assessed in terms of architectural elements and computing resources that have been designed for performance and not necessarily tuned out for RT guarantees. For instance, how well the platform's processor core and memory hierarchy are optimized for average-case performance computing.

**Execution mode switching for mixed workloads:** With this requirement, we want to explain the potentiality of each platform for separating between real-time and non-real-time workloads, which enables the system to handle multiple context switches between high-performance and predictable execution modes at run time. This is not available in many processors and platforms to the best of our knowledge, but we aim to provide a processor that fulfills this requirement.

#### 2.3 Overview of RISC-V ecosystem

Throughout the last decades, large semiconductor companies like INTEL and AMD have dominated the CPU market, which concerns their x86 architectures. Similarly, ARM develops processor designs mainly for mobile devices and microcontrollers. In 2010, RISC-V was born in a lab at the University of California, Berkeley. RISC-V is a new instruction set architecture (ISA) originally designed to support computer architecture research and education. RISC-V evolved a new era of computing on an open and collaborative concept. Recently RISC-V became a standard free and open architecture also for industry implementations [25]. Some fundamental characteristics of RISC-V are simplicity, modularity, stability, and design for specialization. In order to manage the diversity and support the modularity, there are 47 base instructions from 32-bit to 128-bit address space and some optional standard extensions. However, a single fixed ISA spec can not work for all domains.

Currently, there are different RISC-V ISAs as standard extensions available. It is also possible to produce a binary by combining these RISC-V ISA configurations. In the following, different RISC-V ISAs for the 64-bit processors, as an example, have been introduced:

- rv64i for base integer instruction set

- rv64a for atomic memory operations

- rv64f for single-precision floating-point operations

- rv64d for double precision floating-point operations

- rv64m for integer multiplication and division

- rv64c for compressed instructions

For instance, "rv64imac" describes a 64-bit implementation with integer multiplication, atomic memory instructions, and support for compressed instructions.

The specification is divided into two parts: the unprivileged and privileged specifications. The unprivileged specification, also called the user mode ISA, defines general-purpose computational instructions. The privileged ISA describes capabilities used for an operating system or platform level code [26].

#### 2.3.1 Compilers

Regarding the available software toolchain for RISC-V<sup>1</sup>, compiler support for C and C++ is provided through GCC and Clang/LLVM.

$<sup>^1{\</sup>rm A}$  full overview of the RISC-V software ecosystem is available at https://github.com/riscv/riscv-software-list.

The GNU Compiler Collection (GCC) has been the de-facto standard compiler for embedded systems for a long time. The main reason was its support for many embedded processors and microcontrollers and its place as the official compiler for GNU/Linux. The main reason for this success was the open-source model and the support from the GNU/Linux community. Today GCC is one of the most mature compilers for all kinds of computer systems from the embedded to the HPC spectrum. Furthermore, for RISC-V, GCC was the first available compiler and is still the "default" one.

Clang/LLVM [27] is the new "challenger" for GCC. LLVM is an opensource software developed at the University of Illinois/NCSA. The initial version was released in 2003. The name of LLVM was first abbreviated from Low-Level Virtual Machine. Clang is the C, C++, and Objective-C front-end for LLVM. In previous years, back-end support for RISC-V has been added into the Clang/LLVM release [28].

With the availability of two different mature compilers for RISC-V processors, one interesting question is which compiler offers the best performance w.r.t. binary size and execution time. The execution time analysis of the compiled binaries in [29] shows that in 42% of the experiments, GCC and LLVM have nearly the same execution time clock cycles while in 40% GCC execute faster and in 18% LLVM binaries executed faster. Regarding the binary size, in 94% of the experiments, these compilers provide the same binary size. So, in general, the GCC still performs better, and we continue the project with the GCC compiler.

#### 2.3.2 RISC-V CORES

There are many core implementations based on RISC-V ISA available in the market. These processors are either optimized for size and code density [30] or optimized for embedded high-performance computing [3, 31]. Developing 32-bit cores essential for Internet of Thing (IoT) and microcontrollers is much more populated than 64-bit in RISC-V. From the design point of view, the first reason could be the complexity of the 64-bit processor design. The second reason is that it is much more expensive to make 64-bit cores available in

| 3                                                                                                              | 2-bit                                                                                                                        | 64-bit                                                                                                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low cost                                                                                                       | DSP                                                                                                                          | Linux capable                                                                                                                                                                                                           |

| <ul> <li>Zero-riscy <ul> <li>RV32-ICM</li> </ul> </li> <li>Micro-riscy <ul> <li>RV32-CE</li> </ul> </li> </ul> | <ul> <li>RI5CY</li> <li>RV32-ICMFX</li> <li>SIMD</li> <li>HW loops</li> <li>Bit manipulation</li> <li>Fixed point</li> </ul> | <ul> <li>Ariane <ul> <li>RV64-ICMAFD</li> <li>Full privileged specification</li> </ul> </li> <li>Boom <ul> <li>RV64-ICMAFD</li> <li>Full privileged specification</li> <li>Out-of-order pipeline</li> </ul> </li> </ul> |

Table 2.1: RISC-V cores from Low cost to Linux capable cores

silicon or instantiate it on a Field Programmable Gate Array (FPGA). Moreover, supporting the Linux environment for open source implementations is essential for a 64-bit core. Nevertheless, there are several 64-bit cores, e.g., Boom [32, 33] and Ariane [3] available. We focus on the Ariane processor in the rest of this thesis.

### CHAPTER 3

### Related Work

In this chapter, different embedded platforms have been widely investigated. Therefore, this chapter gives an overview of existing platforms that provide solutions for time predictable, high-performance, or both and places them in the context of the work presented in this thesis. In the end, an analysis of the introduced related work platforms will be presented to check the suitability of existing platforms with the concept of switchable architecture design based on the requirements proposed in Section 2.2.2.

#### 3.1 HIGH-PERFORMANCE PLATFORMS

Some embedded high-performance platforms will be reviewed in this section, and their characteristics will be investigated. These platforms are typically available in the embedded system domain if we want to use an embedded high-performance system. Some representations are reviewed here.

#### 3.1.1 ARIANE (CVA6)

Ariane [3] is a processor that is optimized as a low area high-performance class processor in the RISC-V ecosystem. On the other hand, Ariane features support address translation via a Memory Management Unit (MMU) to support an operating system [3]. The processor supports the Linux kernel, but there is no real-time task scheduling in the current version. So, its performance for a comparatively low-area chip is acceptable, but the caches and memory subsystem were not designed for predictability. My approach will introduce predictable execution capabilities to the core. We will also add real-time operating system support for scheduling tasks with different real-time requirements to make it capable of executing tasks with different criticality levels.

#### 3.1.2 RASPBERRY PI 4

The Raspberry Pi 4 [34] consists of ARM Cortex A-series processors with the hierarchy of shared caches and the out-of-order pipeline, which is optimized for average-case performance. So, it is not designed to fulfill the predictability and composability requirements for timing critical workload in a switchable architecture. In this platform, we could integrate a system partitioner using a software layer to separate the cache accesses or install a hypervisor on it to fulfill the predictability requirements to a certain degree but still not fully reach the requirements. So it is not that easy to realize predictable support with the hardware components. The Raspberry Pi supports the operating system but is not out of the box for the scheduling of real-time applications. Therefore, we can easily claim that it is an excellent high-performance platform but not a good option for mixed-criticality environments.

#### 3.1.3 NVIDIA JETSON XAVIER

Regarding NVIDIA Jetson Xavier [35], the explanation about the architecture and the compatibility with the requirements is quite similar to Raspberry Pi plus additional high-performance feature that it has w.r.t its heterogeneity of the embedded Graphics Processing Unit (GPU) inside the architecture. So controlling the accesses and static analysis for predictability is very difficult in such an architecture. Thus, we will not elaborate more about this highperformance platform because it cannot fulfill predictability requirements and support mixed critical workloads.

#### 3.1.4 Zynq 7000

The Zynq 7000 includes Programmable Logic (PL) and Processing System (PS). The exciting feature inside the PL is the potential to implement arbitrary hardware depending on whether we want to customize hardware for timing predictable computation using the Microblaze processor or realize custom hardware accelerators to boost performance. There are also some designs available that successfully developed a mixed timing criticality system using FPGA in Zynq 7000 [36]. Furthermore, regarding the operating system support, Zynq UltraScale+ supports hypervisor or Linux to make shared caches access times more predictable by providing cache partitioning or cache coloring. On the other hand, Zynq UltraScale+ is an Multiprocessor System on a Chip (MPSoC) that inherits the properties of Zynq 7000 plus the so-called safety island design for real-time applications utilizing a dual-core ARM Cortex-R5 based processing system. Regarding the communication times, the system could be composable and predictable due to the globally time-triggered architecture of the NoC, but this requires some manipulations in components. It is possible to support execution mode switching in the Zynq 7000 but not in a single core rather than using both PL and PS parts or in multi-core scenario implementations.

### 3.2 Real-time class platfroms

Some platforms designed to satisfy timing predictability requirements will be reviewed in this section, and their characteristics will be investigated. These platforms are typically available in the embedded system domain if we have tight real-time constraints. Some representations are reviewed here.

#### 3.2.1 CompSoC

CompSoC [37] is being categorized as a system that provides solutions for predictability and composability on a platform level by having a global schedule for the whole system, so we analyze it tile by tile and on the platform level. In order to assess the predictable execution capability, before executing an application on the processor tile, a WCET analysis is done to ensure that the execution time will be within the deadline on the Microblaze processor. The CompSoC platform does not have any cache, but instead, Comp-SoC utilized local Instruction Memory (IMEM) and Data Memory (DMEM) as a predictable solution with the precise size of instruction and data of programs that are allowed to be executed. Of course, this trade-off affects the platform's performance, but this allows the virtual platform to maintain the average case performance and improve the predictability potential. The Network-on-Chip (NoC) of CompSoC is entirely predictable and responsible for transporting requests from the direct memory access unit (DMA) to the off-chip DRAM memory. Another essential component approach in this architecture are predictable memory controllers with a combination of statically and dynamically scheduled Synchronous DRAM (SDRAM) controllers [38]. CompSoC resets the resource state between scheduling intervals. Thus, the interconnects and memory subsystem of the CompSoC are organized to decrease interferences with other communicational elements by controlling the accesses. This makes it slower due to some buffering and WCET estimations but fulfills the composability and predictability requirements in terms of communication times. Regarding operating system support for different criticality tasks, by using a hypervisor-based software approach, a description is annotated to each application code to make it ready to start the execution on a specific physical tile on the virtual platform. Also, CompSoC provides time-triggered scheduling. This causes CompSoC to be able to execute applications with different timing requirements simultaneously [39]. In this multicore platform, the potentiality of processor separation from each other is very important to reduce the probability of interferences. Moreover, this platform can exchange the Microblaze processor with the ARM processor in the tiles to improve the high-performance features of the platform, which is an outstanding feature in multi-core scenarios. In a switchable platform, it could be configured in case of predictable and high-performance computation, which processor gets the priority of accessing the NoC. This architecture puts the processors in independent tiles with independent local memories to avoid the

interferences of the shared memory. If we want to consider it as a platform capable of switching between different modes at run-time, it could be easily available thanks to the software features of the virtual platform. Based on the explained architectural characteristics of the CompSoC virtual platform, it could be understood that the application execution is completely partitioned, so executed applications cannot affect others. Furthermore, the utilization of shared resources for different applications with different criticality levels has been done thanks to the composability of the platform efficiently. The stable software scheduling, predictable hardware design components, and average performance of the processor make this platform a good choice as a run-time switchable platform. The only drawback of CompSoC is that it does not support high-performance execution.

#### 3.2.2 PATMOS

Generally, T-CREST [40] is optimized to be a time-predictable multi-core platform. From the processor point of view, PATMOS is used as the fully predictable core in the T-CREST platform that provides tight integration of the compiler and WCET analysis to enable higher processor utilization [41]. On the other hand, to enable the overall predictability of the whole platform, T-CREST benefits from system partitioning to assign each real-time application a unique execution environment (hardware resources) and avoid other applications using this exclusive hardware. So, the assumption is that there is enough hardware to isolate for executing a program, which is costly but practical. It statically serves the WCET execution time with average performance output and does not waste much performance. PATMOS contains size configurable method, data, and stack caches and two SPMs, but for T-CREST as a multi-core platform, the SPM usage is under MOSSCA operating system control [42]. Regarding operating system support, the TDMA based memory access arbitration is used for fair and predictable accessing the controller. Moreover, a combination of the time-predictable memory tree and the time-predictable memory controller is needed on a multi-core system. T-CREST interconnects consist of predictable NoC, which is used to communicate between processors to enable time-predictable usage of a shared resource. Thus, PATMOS features the first four requirements because the processor has enough potential as an average case performance and a fully predictable processor. Hardware-based isolation is considered as a secure solution for predictability and also, in this case, provides good performance. The only drawback is that it is not the case in many other architectures due to hardware resources limitations. In addition, the PATMOS pipeline is configurable to be either a standard dual-issue for good performance without the unpredictability of dynamic instruction issuing or a single issue to occupy less area. Since T-CREST has been designed as a fully predictable platform, it does not support switching for mixed workloads. However, PATMOS is applicable to be a switchable platform due to its predictability and performance features, among many other available architectures. Nevertheless, it should be considered that this implementation is costly and also requires some modifications to separate between mixed HP and RT workloads.

#### 3.2.3 FLEXPRET

FlexPRET [43] is a 32-bit, 5-stage, a fine-grained multithreaded processor with software-controlled, flexible thread scheduling. It employs a classical RISC 5-stage pipeline with instruction fetch (F), decode (D), execute (E), memory (M), and writeback (W). FlexPRET naturally offers running softreal-time and hard-real-time workloads in parallel. It supports an arbitrary interleaving of threads, controlled by a thread scheduler in a mixed-criticality system to reduce hardware costs. Applications executed in a hard real-time thread execute in predictable and reproducible time. Furthermore, for these threads, the execution times are composable because FlexPRET utilized hardware-based isolation for these HRTTs, so this is an excellent example of self composability inside the pipeline. Another aspect of FlexPRET is using instruction and data SPMs to avoid the unpredictability issues of the caches. Since FlexPRET is only a processor core and not an entire platform, no statement can be made concerning the properties of the communication times. One solution for operating system support for task scheduling could have been software-based isolation provided by an RTOS, but the operating system support is not available so far. Compared with a predictable PATMOS processor in the T-CREST platform, FlexPRET supports executing tasks with lower predictability using soft real-time threads and avoids underutilization of resources. The overall performance of this processor is limited by the in-order pipeline design. In addition, the execution mode switching is available for hard and soft real-time applications and not for high-performance and real-time applications.

#### 3.2.4 SPEAR

SPEAR consists of a 16-bit processor core with three pipeline stages to achieve reasonable performance; however, in SPEAR2 [44] the performance feature is improved by adding memory stage to the pipeline, but it is still far from performance optimizations. The goal of SPEAR architecture is deterministic timing behavior within the processor core. Moreover, SPEAR offers a constant one-clock cycle execution time for each instruction by avoiding all pipeline data and control hazards to keep the processor predictable. It fulfills the predictability of execution time requirement. Since it is a single processor that is optimized only for hard real-time workloads, the composability features and predictability for communication purposes are not available. Regarding the memory architecture, there are 4kB data and four kB instructions on-chip memories and external caches. SPEAR neither supports an operating system nor a switching environment for mixed workloads. Although SPEAR has a highly efficient architecture suitable for hard realtime applications, it needs more optimization in the memory subsystem in order to increase the capability of utilizing it for some average-performance workloads.

# 3.3 Analysis of suitability of existing platforms for switchable architecture design

In Section 2.2.2 the requirements for switchable processor design were demonstrated. As a general assessment, we have provided Table 3.1 to check for the processor whether it fulfills each specific requirement or not. In this regard, we introduced a scoring scheme to clarify to what extent they fulfill each requirement. Therefore, ++ is assigned to a processor that completely fulfills that requirement without needing any other modification in the microarchitectures or software level. + assigned to a processor capable of fulfilling that requirement but with minor modification and - is for the platform that does not perform well on that requirement. Finally, for the platforms that corresponding requirement is not defined or is not possible to progress in the sense of that requirement na assigned as not applicable.